- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378446 > CH7006C-T (Electronic Theatre Controls, Inc.) Circular Connector; Body Material:Aluminum; Series:PT06; Number of Contacts:18; Connector Shell Size:14; Connecting Termination:Crimp; Circular Shell Style:Straight Plug; Circular Contact Gender:Socket; Insert Arrangement:14-18 PDF資料下載

參數(shù)資料

| 型號(hào): | CH7006C-T |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | 圓形連接器 |

| 英文描述: | Circular Connector; Body Material:Aluminum; Series:PT06; Number of Contacts:18; Connector Shell Size:14; Connecting Termination:Crimp; Circular Shell Style:Straight Plug; Circular Contact Gender:Socket; Insert Arrangement:14-18 |

| 中文描述: | 數(shù)字電視編碼器電腦功能 |

| 文件頁(yè)數(shù): | 35/49頁(yè) |

| 文件大小: | 338K |

| 代理商: | CH7006C-T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)

201-0000-026 Rev 2.1, 8/2/99

35

CHRONTEL

CH7006C

Register Descriptions

(continued)

Note:

For what was formerly defined as the master mode, the user must now externally connect the P-OUT clock to the

XCLK input pin. Although it is possible to set the XCM [1:0] and PCM[1:0] values independent of the input data format,

there are only certain combinations of input data format, XCM and PCM, that will result in valid data being demultiplexed

at the input of the device. Refer to the “Input Data Format Register” for these combinations.

Note:

Display modes 25 and 26 must use a 2X multiplexed input data format and a 2X XCLK. Display modes 27

and 28 must use a 1X XCLK input data format.

The Clock Mode Register also contains the following bits:

MCP (bit 4) determines which edge of the pixel clock output will be used to latch input data. Zero selects the

negative edge, one selects the positive edge.

M/S* (bit 6) determines whether the device operates in master or slave clock mode. In master mode (1), the

14.31818MHz clock is used as a frequency reference to the PLL. In slave mode (0) the XCLK input is used as

a reference to the PLL, and is divided by the value specified by XCM[1:0]. The divide by N and M are forced

to one.

CFRB (bit 7) sets whether the chroma subcarrier free-runs, or is locked to the video signal. One causes the

subcarrier to lock to the TV vertical rate, and should be used when the ACIV bit is set to zero. Zero causes the

subcarrier to free-run, and should be used when the ACIV bit is set to one.

Start Active Video Register

Symbol: SAV

Address: 07H

Bits: 8

This register sets the delay in pixel increments from leading edge of horizontal sync, or the rising edge of data start,

to the start of active video. The entire bit field SAV[8:0] is comprised of this register SAV[7:0], plus the MSB value

contained in the position overflow register, bit SAV8. This is decoded as a whole number of pixels, which can be

set anywhere between 0 and 511 pixels. Therefore, in any 2X clock mode, the number of 2X clocks from the

leading edge of sync to the first active data must be a multiple of two clocks. In any 3X clock mode, the number of

3X clocks from the leading edge of sync to the first active data must be a multiple of three clocks. When using the

DS/BCO pin as a data start input, this register should be set to decimal value 11.

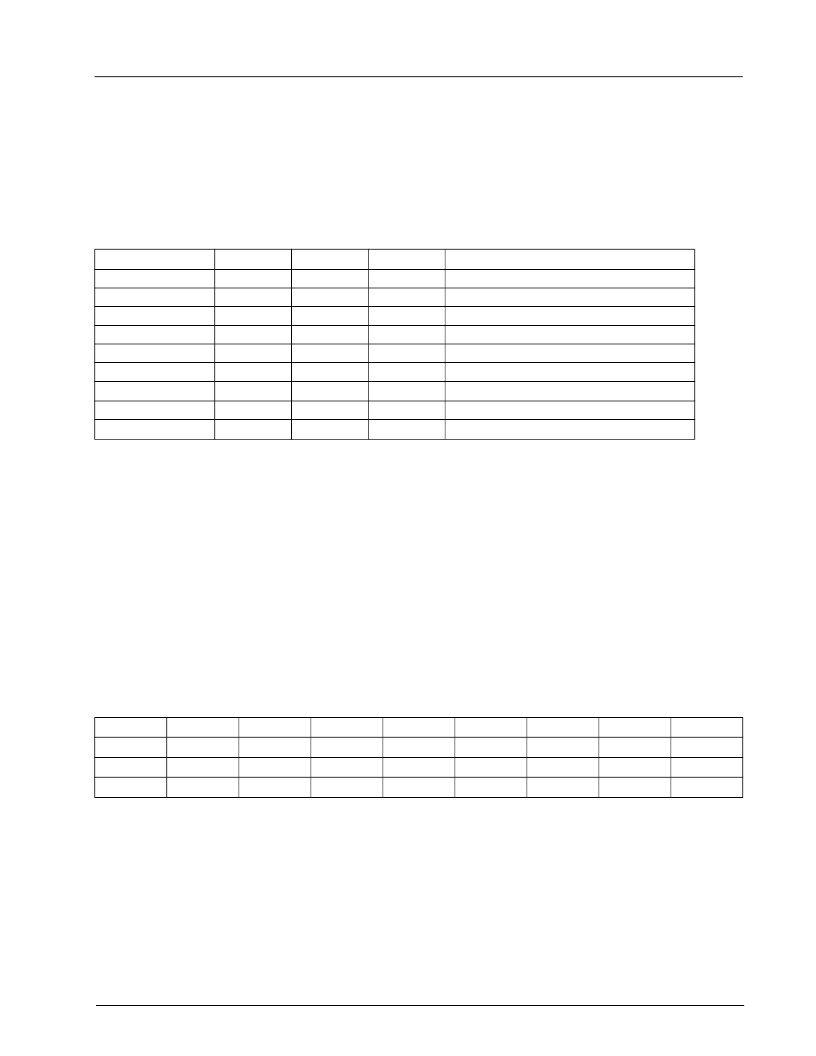

Table 21. Input Data Format Register

XCM[1:0]

00

00

00

01

01

01

1X

PCM[1:0]

00

01

1X

00

01

1X

00

XCLK

1X

1X

1X

2X

2X

2X

3X

P-OUT

1X

2X

3X

1X

2X

3X

1X

Input Data Modes Supported

0, 1, 2, 3, 4, 5, 7, 8, 9

0, 1, 2, 3, 4, 5, 7, 8, 9

0, 1, 2, 3, 4, 5, 7, 8, 9

2, 4, 5, 7, 8, 9

2, 4, 5, 7, 8, 9

2, 4, 5, 7, 8, 9

6

6

6

1X

01

1X

3X

3X

2X

3X

1X

Bit:

7

SAV7

6

SAV6

5

SAV5

4

SAV4

3

SAV3

2

SAV2

1

SAV1

0

SAV0

Symbol:

Type:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default:

0

0

0

0

0

0

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CH7006C-V | Circular Connector; Body Material:Aluminum; Series:PT06; No. of Contacts:18; Connector Shell Size:14; Connecting Termination:Crimp; Circular Shell Style:Straight Plug; Circular Contact Gender:Socket; Insert Arrangement:14-18 |

| CH7013A | Digital PC to TV Encoder |

| CH7013A-T | Digital PC to TV Encoder |

| CH7013A-V | Digital PC to TV Encoder |

| CHB1143 | CHB1143 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CH7006C-V | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital PC to TV Encoder Features |

| CH7007A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DIGITAL PC TO TV ENCODER WITH MACROVISION |

| CH7007A-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DIGITAL PC TO TV ENCODER WITH MACROVISION |

| CH7007A-V | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DIGITAL PC TO TV ENCODER WITH MACROVISION |

| CH7008A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital PC to TV Encoder Features |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。