- 您現(xiàn)在的位置:買賣IC網 > PDF目錄378445 > CH5101A (Electronic Theatre Controls, Inc.) CMOS Monochrome Digital Video Camera PDF資料下載

參數資料

| 型號: | CH5101A |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | CMOS Monochrome Digital Video Camera |

| 中文描述: | 單色的CMOS數碼攝像機 |

| 文件頁數: | 14/32頁 |

| 文件大小: | 132K |

| 代理商: | CH5101A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

14

201-0000-033 Rev 1.0, 6/2/99

CHRONTEL

CH5101A

that, the master may read another data byte and so on. In summary, a RESTART condition, followed by a DAB,

must be produced by the master before each of the RAB and before each of the data read events.

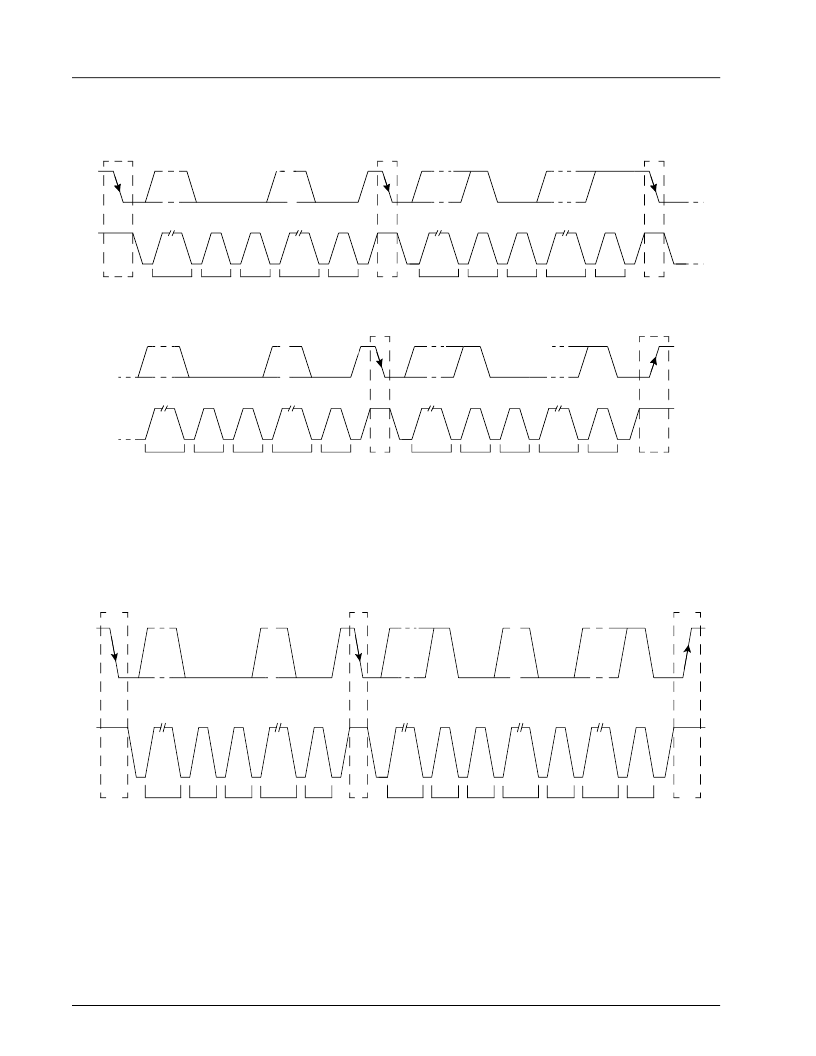

Figure 10

shows

two

consecutive alternating read cycles.

Figure 10: Alternating Read Cycle

If AutoInc = 1, then the address register will be incremented automatically and subsequent data bytes can be read

from successive registers, without providing a second RAB

Figure 11: Auto-increment Read Cycle

When the auto-increment mode is enabled (AutoInc is set to 1), the address register will continue incrementing for

each read cycle. When the content of the Address Register reaches 2A, it will wrap around and start from 00h again.

The auto increment sequence can be terminated by either a STOP or RESTART condition. The read operation can

be terminated with a “STOP” condition.

Figure 11

shows an auto-increment read cycle terminated by a STOP or

RESTART condition.The CH5101 contains 20 control registers each with a maximum of 8 usable bits to provide

access to basic video attribute control functions. These registers are accessible via the 2-bit serial bus (SD & SC).

The following sections describe the functions and the controls available through these registers.

SD

SC

1 - 8

RAB 1

9

10

ACK

Restart

Condition

Condition

Start

Condition

Stop

Master does

not acknowledge

1 - 7

Device

8

R/W*

9

ACK

CH5101

acknowledge

CH5101

acknowledge

1 - 8

Data 1

9

ACK

1 - 7

Device

8

R/W*

9

ACK

CH5101

acknowledge

I

2

C

10

Restart

Condition

1 - 8

RAB 2

9

10

ACK

Restart

Condition

1 - 7

Device ID

8

R/W*

9

ACK

CH5101

acknowledge

1 - 8

Data 2

9

ACK

1 - 7

Device ID

8

R/W*

9

ACK

CH5101

acknowledge

I

2

C

I

2

C

Master

does not

acknowledge

CH5101

acknowledge

Master

acknowledge

SD

SC

1 - 8

RAB n

9

10

ACK

Restart

Condition

Condition

Start

Condition

Stop

Master does

not acknowledge

just before Stop

condition

1 - 7

Device

8

R/W*

9

ACK

CH5101

acknowledge

CH5101

acknowledge

1 - 8

Data n

9

ACK

1 - 7

Device

8

R/W*

9

ACK

CH5101

acknowledge

1 - 8

Data

n+1

9

ACK

I

2

C

I

2

C

相關PDF資料 |

PDF描述 |

|---|---|

| CH5101A-L | CMOS Monochrome Digital Video Camera |

| CH7003B-T | Digital PC to TV Encoder |

| CH7003B | Digital PC to TV Encoder |

| CH7003B-V | Digital PC to TV Encoder |

| CH7006C | MODULE |

相關代理商/技術參數 |

參數描述 |

|---|---|

| CH5101A-L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Monochrome Digital Video Camera |

| CH5101A-Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CMOS Monochrome Digital Video Camera |

| CH511H-30PT | 制造商:CHENMKO 制造商全稱:Chenmko Enterprise Co. Ltd. 功能描述:SCHOTTKY BARRIER DIODE VOLTAGE 30 Volts CURRENT 1.0 Ampere |

| CH511H-40PT | 制造商:CHENMKO 制造商全稱:Chenmko Enterprise Co. Ltd. 功能描述:SCHOTTKY BARRIER DIODE VOLTAGE 40 Volts CURRENT 1.0 Ampere |

| CH5125C6W | 制造商:Cooper Crouse-Hinds 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。