- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378439 > CCU3000 (MICRONAS SEMICONDUCTOR HOLDING AG) Central Control Unit PDF資料下載

參數(shù)資料

| 型號: | CCU3000 |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Central Control Unit |

| 中文描述: | MICROCONTROLLER, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 10/77頁 |

| 文件大?。?/td> | 837K |

| 代理商: | CCU3000 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

CCU 3000, CCU 3000-I

CCU 3001, CCU 3001-I

MICRONAS INTERMETALL

10

2.11. Interrupt Controller

The most important properties of this controller are:

– 8 sources

– 8 freely programmable priorities for every source

– maximum delay of 3 clock cycles

– vectorized interrupts, i.e., automatically the correct

routine is accessed

– also to be used for external CPU

– option: disable after interrupt (resettable by software)

Running service routines are only interrupted if inter-

rupts are enabled and a request of higher priority arrives.

All others are stored and executed when interrupts of

higher priority have been finished. Priority 0 means that

the corresponding interrupt is disabled. (Priorities 1-7

lead to interrupts). One property of the controller is that

the CPU is not modified, but vectorization takes place all

the same. Thus the use of this controller is also possible

for external CPUs (emulator!).

Solely the return from a service program differs slightly

in software from the methods normally used for the

65C02. The last command before the “RTI” must be a

write operation into the return register of the controller.

This tells the controller that the service routine has been

completed. Apart from this return register the controller

occupies further 5 bytes. One of these serves as a con-

trol byte, the others incorporate the priorities for 8

sources. The controller therefore needs 6 bytes of the

I/O-page. The control byte comprises:

bit 0

bit 1

bit 2

bit 3

bit 4

CLEAR_ALL_REQUESTS

ALLOW_ONE_INTERRUPT

DISABLE_INTERRUPTS

DISABLE_AFTER_INT

RESET_CONTROLLER

(low active)

(low active)

(low active)

(low active)

(low active)

All bits reset to 1 (inactive).

CLEAR_ALL_REQUESTS clears all interrupt flags at

the same time. ALLOW_ONE_INTERRUPT is used in

connection with the DISABLE_AFTER_INT (bit 3), to al-

low access to the next interrupt. DISABLE_INTERRUPT

does not allow any interrupts, the request flags are set

however. With the exception of bits 3 and 2 (DIS-

ABLE_INTERRUPTS, DISABLE_AFTER_INT) these

are all dynamic signals, that is, the write process itself

sends an appropriate signal. This has the same impulse

length as the 65C02. Each of the 4 priority registers con-

tains the priorities for 2 interrupt sources.

bit 7, 6, 5, 4

bit 3, 2, 1, 0 Priority for sources

Priority for sources

8, 6, 4, 2

7, 5, 3, 1

To connect an external CPU (emulator) with the control-

ler, only two ICs of the 74-family are needed.

ADB

DB

CTRLQ

Φ

2

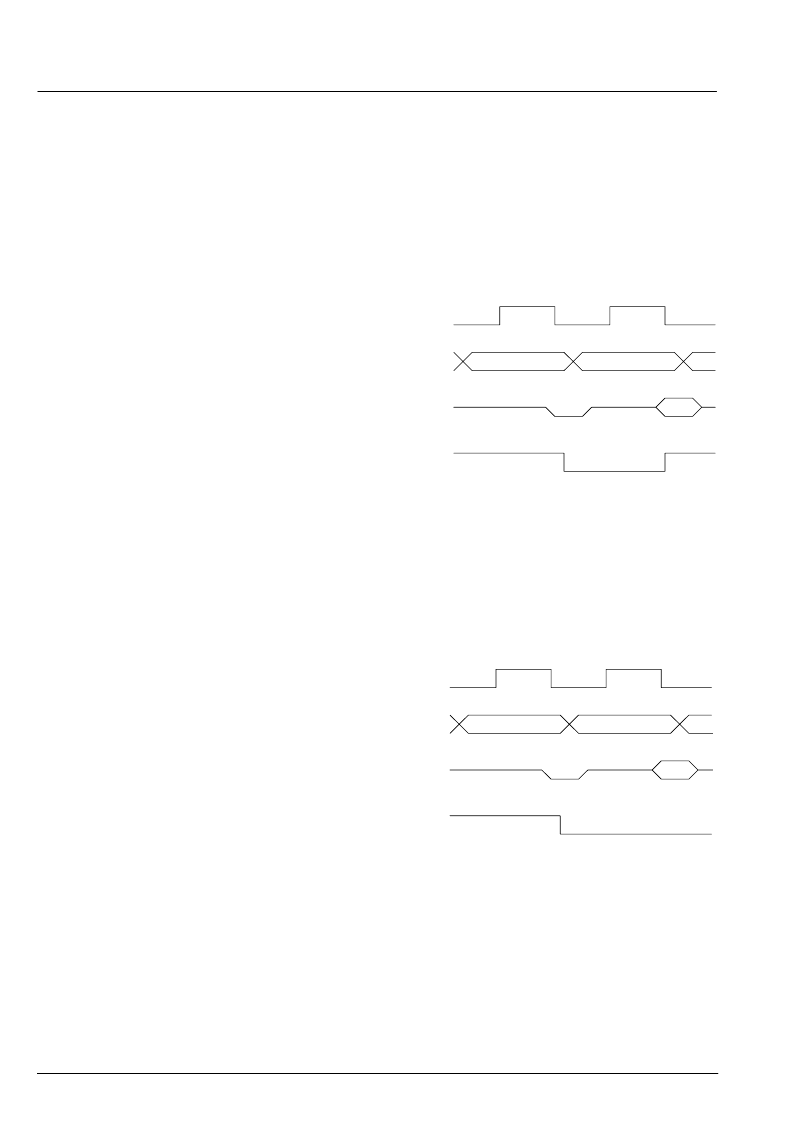

Fig. 2–9:

Dynamic control signals interrupt

Bits 0, 1, 4

ADB

DB

CTRLQ

Φ

Fig. 2–10:

Static control signals interrupt

Bits 2, 3

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CCU3000-I | Central Control Unit |

| CCU3001 | Central Control Unit |

| CCU3001-I | Central Control Unit |

| CD-700-KAC-GAB-XX.XXX | Complete VCXO Based Phase Lock Loop |

| CD-700-LAF-GGB-XX.XXX | Complete VCXO Based Phase Lock Loop |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CCU3000I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CCU3000-I | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Central Control Unit |

| CCU3001 | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Central Control Unit |

| CCU3001I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CCU3001-I | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Central Control Unit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。