- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366766 > CAT93C56XAT3E The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each PDF資料下載

參數(shù)資料

| 型號: | CAT93C56XAT3E |

| 元件分類: | EEPROM |

| 英文描述: | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 中文描述: | 該CAT24FC02是一個2 KB的EEPROM的國內(nèi)256個8位每字舉辦的串行CMOS |

| 文件頁數(shù): | 6/9頁 |

| 文件大小: | 420K |

| 代理商: | CAT93C56XAT3E |

6

CAT93C56/57

Doc. No. 1088, Rev. O

Erase

Upon receiving an ERASE command and address, the

CS (Chip Select) pin must be deasserted for a minimum

of t

CSMIN

. The falling edge of CS will start the self clocking

clear cycle of the selected memory location. The clocking

of the SK pin is not necessary after the device has

entered the self clocking mode. The ready/busy status of

the CAT93C56/57 can be determined by selecting the

device and polling the DO pin. Once cleared, the content

of a cleared location returns to a logical

“

1

”

state.

Erase/Write Enable and Disable

The CAT93C56/57 powers up in the write disable state.

Any writing after power-up or after an EWDS (write

disable) instruction must first be preceded by the EWEN

(write enable) instruction. Once the write instruction is

enabled, it will remain enabled until power to the device

is removed, or the EWDS instruction is sent. The EWDS

instruction can be used to disable all CAT93C56/57

write and clear instructions, and will prevent any

accidental writing or clearing of the device. Data can be

read normally from the device regardless of the write

enable/disable status.

Erase All

Upon receiving an ERAL command, the CS (Chip Select)

pin must be deselected for a minimum of t

CSMIN

. The

falling edge of CS will start the self clocking clear cycle

of all memory locations in the device. The clocking of the

SK pin is not necessary after the device has entered the

self clocking mode. The ready/busy status of the

CAT93C56/57 can be determined by selecting the device

and polling the DO pin. Once cleared, the contents of all

memory bits return to a logical

“

1

”

state.

Write All

Upon receiving a WRAL command and data, the CS

(Chip Select) pin must be deselected for a minimum of

t

CSMIN

. The falling edge of CS will start the self clocking

data write to all memory locations in the device. The

clocking of the SK pin is not necessary after the device

has entered the self clocking mode. The ready/busy

status of the CAT93C56/57 can be determined by

selecting the device and polling the DO pin. It is not

necessary for all memory locations to be cleared before

the WRAL command is executed.

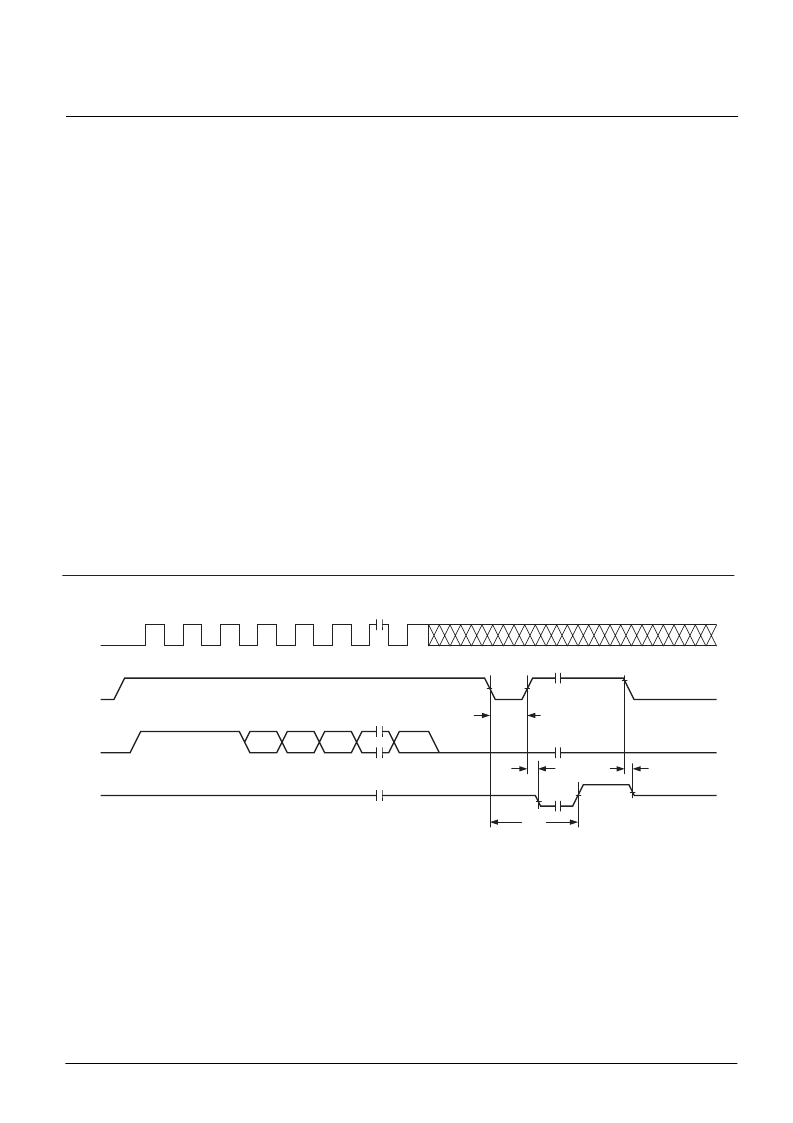

Figure 4. Erase Instruction Timing

SK

CS

DI

DO

STANDBY

HIGH-Z

HIGH-Z

1

AN

AN-1

BUSY

READY

STATUS VERIFY

tSV

tHZ

tEW

tCS

1

1

A0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT93C56XE-1.8-GT2E | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| CAT93C56XE-1.8-GT3E | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| CAT93C56XE-1.8T2E | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| CAT93C56XE-1.8T3E | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| CAT93C56XE-GT2E | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT93C56XA-TE13 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| CAT93C56XE | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:2K-Bit Microwire Serial EEPROM |

| CAT93C56XE-1.8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| CAT93C56XE-1.8-GT2E | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:2-Kb Microwire Serial CMOS EEPROM |

| CAT93C56XE-1.8-GT3E | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:2-Kb Microwire Serial CMOS EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。