- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366709 > CAT25C128LET2 128K/256K-Bit SPI Serial CMOS EEPROM PDF資料下載

參數(shù)資料

| 型號: | CAT25C128LET2 |

| 英文描述: | 128K/256K-Bit SPI Serial CMOS EEPROM |

| 中文描述: | 128K/256K-Bit SPI串行EEPROM中的CMOS |

| 文件頁數(shù): | 7/12頁 |

| 文件大小: | 454K |

| 代理商: | CAT25C128LET2 |

7

CAT25C128/256

Document No. 1018, Rev. I

The WPEN (Write Protect Enable) is an enable bit for the

WP

pin. The

WP

pin and WPEN bit in the status register

control the programmable hardware write protect fea-

ture. Hardware write protection is enabled when

WP

is

low and WPEN bit is set to high. The user cannot write

to the status register (including the block protect bits and

the WPEN bit) and the block protected sections in the

memory array when the chip is hardware write pro-

tected. Only the sections of the memory array that are

not block protected can be written. Hardware write

protection is disabled when either WP pin is high or the

WPEN bit is zero.

DEVICE OPERATION

Write Enable and Disable

The CAT25C128/256 contains a write enable latch. This

latch must be set before any write operation. The device

powers up in a write disable state when V

cc

is applied.

WREN instruction will enable writes (set the latch) to the

device. WRDI instruction will disable writes (reset the

latch) to the device. Disabling writes will protect the

device against inadvertent writes.

READ Sequence

The part is selected by pulling

CS

low. The 8-bit read

instruction is transmitted to the CAT25C128/256, followed

by the 16-bit address(the three Most Significant Bit is

don’t care for 25C256 and four most significant bits are

don't care for 25C128).

After the correct read instruction and address are sent,

the data stored in the memory at the selected address is

shifted out on the SO pin. The data stored in the memory

at the next address can be read sequentially by continuing

to provide clock pulses. The internal address pointer is

automatically incremented to the next higher address

after each byte of data is shifted out. When the highest

address (7FFFh for 25C256 and 3FFFh for 25C128) is

reached, the address counter rolls over to 0000h allowing

the read cycle to be continued indefinitely. The

readoperation is terminated by pulling the

CS

high.

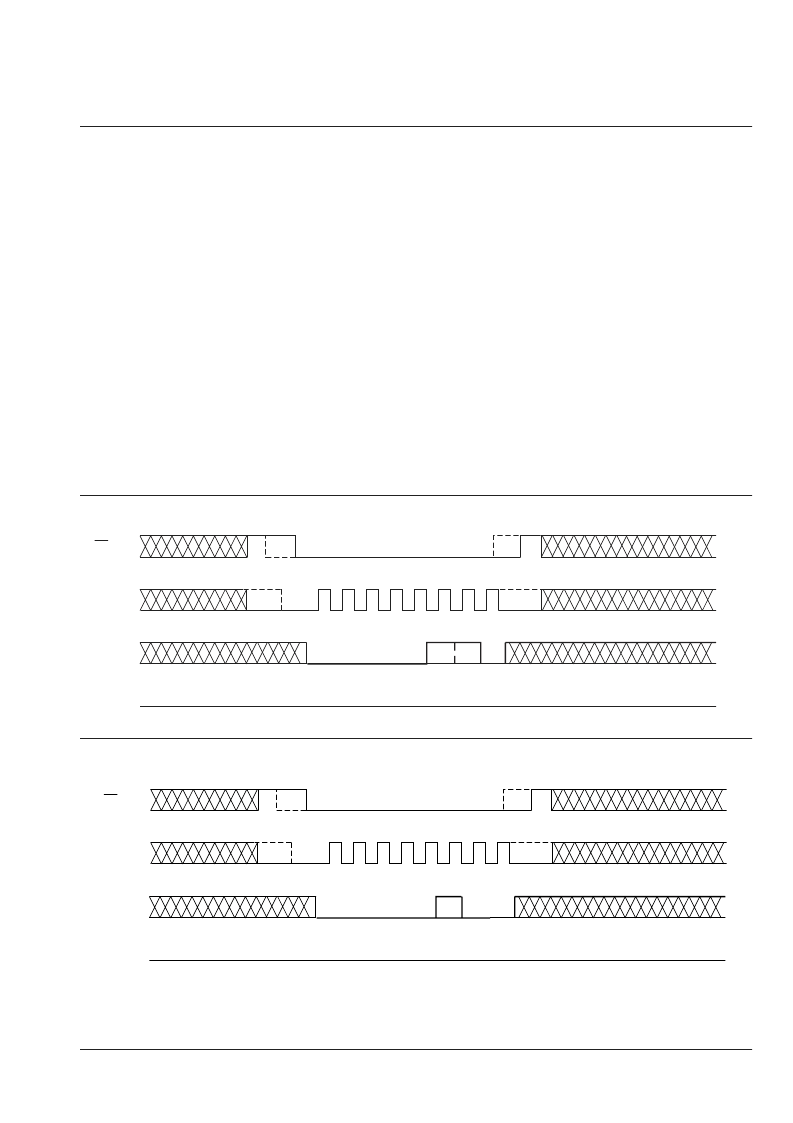

SK

SI

CS

SO

0

0

0

0

0

1

1

0

HIGH IMPEDANCE

Figure 2. WREN Instruction Timing

SK

SI

CS

SO

0

0

0

0

0

1

0

0

HIGH IMPEDANCE

Note: Dashed Line= mode (1, 1) — — — —

Figure 3. WRDI Instruction Timing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT25C128LET3 | 128K/256K-Bit SPI Serial CMOS EEPROM |

| CAT25C128L-GT2 | 128K/256K-Bit SPI Serial CMOS EEPROM |

| CAT25C128L-GT3 | 128K/256K-Bit SPI Serial CMOS EEPROM |

| CAT25C128LI-1.8-GT2 | 128K/256K-Bit SPI Serial CMOS EEPROM |

| CAT25C128LI-1.8-GT3 | 128K/256K-Bit SPI Serial CMOS EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT25C128LI | 功能描述:電可擦除可編程只讀存儲器 (16kx8) 128K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT25C128LI-G | 功能描述:電可擦除可編程只讀存儲器 (16384x8) 128K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT25C128P | 功能描述:電可擦除可編程只讀存儲器 (16kx8) 128K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT25C128P-1.8 | 功能描述:電可擦除可編程只讀存儲器 (16kx8) 128K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| CAT25C128PA | 功能描述:電可擦除可編程只讀存儲器 (16kx8) 128K RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。