- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369653 > CAT22C10PI-30-TE13 256-Bit Nonvolatile CMOS Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | CAT22C10PI-30-TE13 |

| 英文描述: | 256-Bit Nonvolatile CMOS Static RAM |

| 中文描述: | 256位非易失性的CMOS靜態(tài)RAM |

| 文件頁(yè)數(shù): | 6/10頁(yè) |

| 文件大小: | 514K |

| 代理商: | CAT22C10PI-30-TE13 |

CAT22C10

6

Doc. No. 1082, Rev. O

DEVICE OPERATION

The configuration of the CAT22C10 allows a common

address bus to be directly connected to the address

inputs. Additionally, the Input/Output (I/O) pins can be

directly connected to a common I/O bus if the bus has

less than 1 TTL load and 100pF capacitance. If not, the

I/O path should be buffered.

When the chip select (

CS

) pin goes low, the device is

activated. When CS is forced high, the device goes into

the standby mode and consumes very little current. With

the nonvolatile functions inhibited, the device operates

like a Static RAM. The Write Enable (

WE

) pin selects a

write operation when

WE

is low and a read operation

when

WE

is high. In either of these modes, an array byte

(4 bits) can be addressed uniquely by using the address

lines (A

0

–A

5

), and that byte will be read or written to

through the Input/Output pins (I/O

0

–I/O

3

).

The nonvolatile functions are inhibited by holding the

STORE

input and the

RECALL

input high. When the

RECALL

input is taken low, it initiates a recall operation

which transfers the contents of the entire EEPROM

array into the Static RAM. When the

STORE

input is

taken low, it initiates a store operation which transfers

the entire Static RAM array contents into the EEPROM

array.

Standby Mode

The chip select (

CS

) input controls all of the functions of

the CAT22C10. When a high level is supplied to the

CS

pin, the device goes into the standby mode where the

outputs are put into a high impendance state and the

power consumption is drastically reduced. With I

SB

less

than 100

μ

A in standby mode, the designer has the

flexibility to use this part in battery operated systems.

Read

When the chip is enabled (

CS

= low), the nonvolatile

functions are inhibited (

STORE

= high and

RECALL

=

high). With the Write Enable (

WE

) pin held high, the data

in the Static RAM array may be accessed by selecting an

address with input pins A

0

–A

. This will occur when the

outputs are connected to a bus which is loaded by no

more than 100pF and 1 TTL gate. If the loading is greater

than this, some additional buffering circuitry is recom-

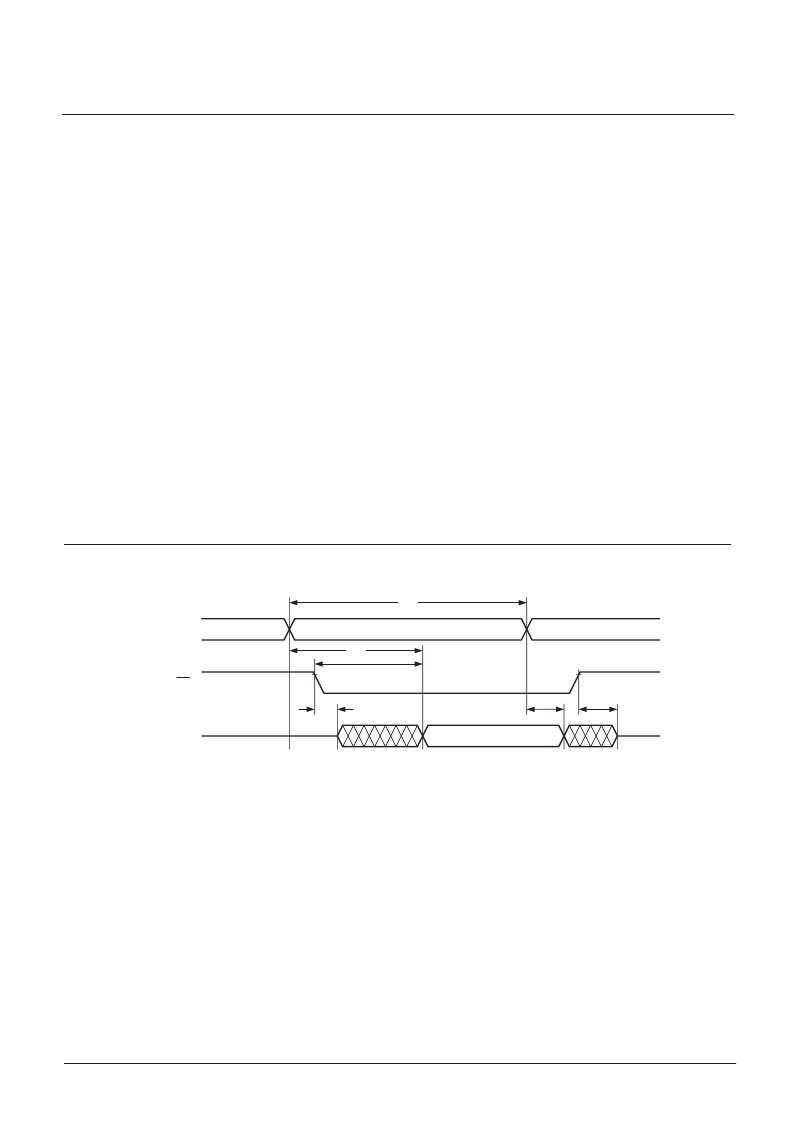

Figure 1. Read Cycle Timing

ADDRESS

CS

DATA I/O

tRC

tCO

tAA

tLZ

tOH

tHZ

HIGH-Z

DATA VALID

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT22C10W-20-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10W-30-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10WA-20-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10WA-30-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10WI-20-TE13 | 256-Bit Nonvolatile CMOS Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT22C10W-20 | 制造商:ON Semiconductor 功能描述:256-BIT N V CMOS STATIC RAM - Rail/Tube |

| CAT22C10W-20TE13 | 制造商:ON Semiconductor 功能描述:256-BIT N V CMOS STATIC RAM - Tape and Reel |

| CAT22C10W-20-TE13 | 制造商:CATALYST 制造商全稱(chēng):Catalyst Semiconductor 功能描述:256-Bit Nonvolatile CMOS Static RAM |

| CAT22C10W-30 | 制造商:ON Semiconductor 功能描述:256-BIT N V CMOS STATIC RAM - Rail/Tube |

| CAT22C10W-30TE13 | 制造商:ON Semiconductor 功能描述:256-BIT N V CMOS STATIC RAM - Tape and Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。