- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366663 > CAT1024LI-42-GT2 Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset PDF資料下載

參數(shù)資料

| 型號(hào): | CAT1024LI-42-GT2 |

| 英文描述: | Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| 中文描述: | 監(jiān)控電路,帶有I2C串行的2K位CMOS EEPROM和手動(dòng)復(fù)位 |

| 文件頁(yè)數(shù): | 9/20頁(yè) |

| 文件大?。?/td> | 267K |

| 代理商: | CAT1024LI-42-GT2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

CAT1024, CAT1025

2007 Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

9

Doc. No. 3008 Rev. N

EMBEDDED EEPROM OPERATION

The CAT1024 and CAT1025 feature a 2-kbit embedded

serial EEPROM that supports the I

2

C Bus data

transmission protocol. This Inter-Integrated Circuit Bus

protocol defines any device that sends data to the bus to

be a transmitter and any device receiving data to be a

receiver. The transfer is controlled by the Master device

which generates the serial clock and all START and

STOP conditions for bus access. Both the Master device

and Slave device can operate as either transmitter

or receiver, but the Master device controls which mode

is activated.

I

2

C BUS PROTOCOL

The features of the I

2

C bus protocol are defined as

follows:

(1) Data transfer may be initiated only when the bus

is not busy.

(2) During a data transfer, the data line must remain

stable whenever the clock line is high. Any

changes in the data line while the clock line is

high will be interpreted as a START or STOP

condition.

START CONDITION

The START Condition precedes all commands to the

device, and is defined as a HIGH to LOW transition of

SDA when SCL is HIGH. The CAT1024/25 monitors

the SDA and SCL lines and will not respond until this

condition is met.

STOP CONDITION

A LOW to HIGH transition of SDA when SCL is HIGH

determines the STOP condition. All operations must

end with a STOP condition.

DEVICE ADDRESSING

The Master begins a transmission by sending a

START condition. The Master sends the address of

the particular slave device it is requesting. The four

most significant bits of the 8-bit slave address are

programmable in metal and the default is 1010.

The last bit of the slave address specifies whether a

Read or Write operation is to be performed. When this

bit is set to 1, a Read operation is selected, and when

set to 0, a Write operation is selected.

After the Master sends a START condition and the

slave address byte, the CAT1024/25 monitors the bus

and responds with an acknowledge (on the SDA line)

when its address matches the transmitted slave

address. The CAT1024/25 then perform a Read or

Write operation depending on the R/ˉˉ bit.

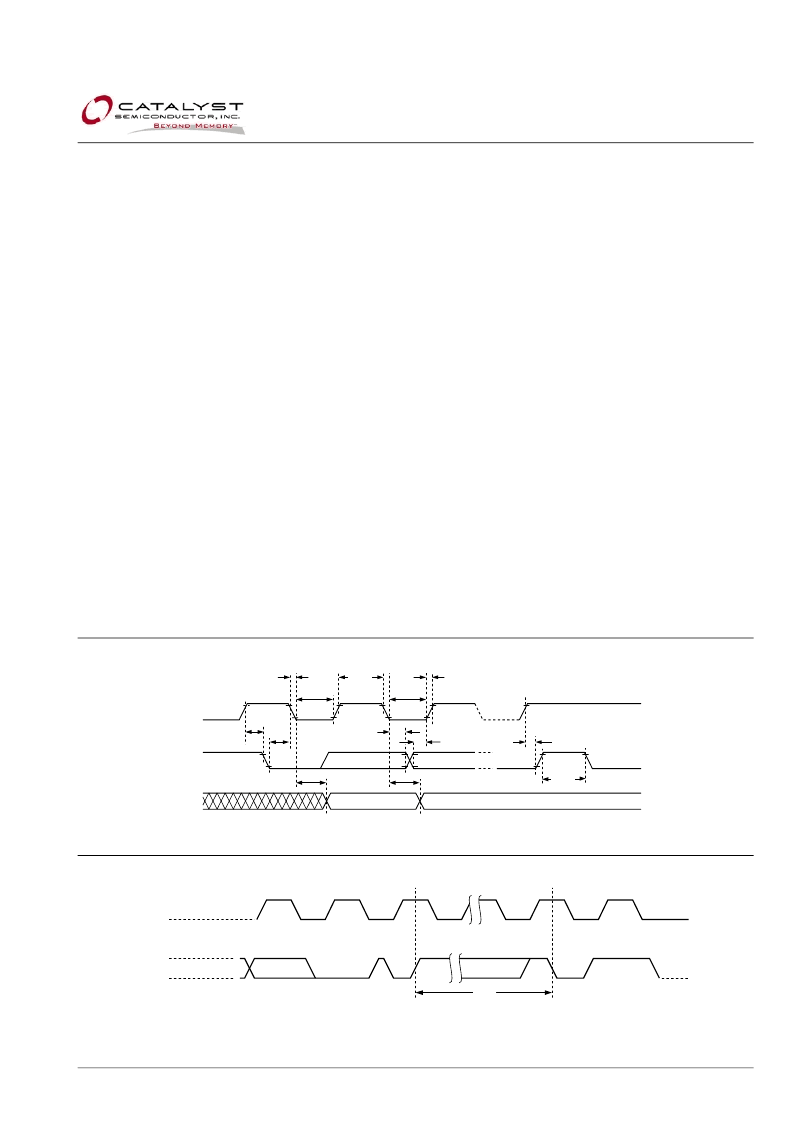

Figure 3. Bus Timing

Figure 4. Write Cycle Timing

tHIGH

SCL

SDA IN

SDA OUT

tLOW

tF

tLOW

tR

tBUF

tSU:STO

tSU:DAT

tHD:DAT

tHD:STA

tSU:STA

tAA

tDH

tWR

STOP

CONDITION

START

CONDITION

ADDRESS

ACK

8TH BIT

BYTE n

SCL

SDA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT1024LI-42-GT3 | Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024LI-42T2 | Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024LI-42T3 | Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024LI-45 | Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024LI-45-GT2 | Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT1024LI-42-GT3 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024LI-42T2 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024LI-42T3 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024LI-42TE13 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset |

| CAT1024LI45 | 功能描述:監(jiān)控電路 2K bit 4.5V Ind Temp RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過(guò)電壓閾值: 輸出類(lèi)型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開(kāi)關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。