- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄257720 > CAT1022WI-28 (ON SEMICONDUCTOR) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO8 PDF資料下載

參數(shù)資料

| 型號: | CAT1022WI-28 |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 電源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO8 |

| 封裝: | 0.150 INCH, HALOGEN FREE AND ROHS COMPLIANT, MS-012, SOIC-8 |

| 文件頁數(shù): | 2/21頁 |

| 文件大小: | 307K |

| 代理商: | CAT1022WI-28 |

CAT1021, CAT1022, CAT1023

Doc. No. 3009 Rev. L

10

2007 Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

ACKNOWLEDGE

After a successful data transfer, each receiving

device is required to generate an acknowledge. The

acknowledging device pulls down the SDA line

during the ninth clock cycle, signaling that it received

the 8 bits of data.

All devices respond with an acknowledge after

receiving a START condition and its slave address.

If the device has been selected along with a write

operation, it responds with an acknowledge after

receiving each 8-bit byte.

When a device begins a READ mode it transmits 8

bits of data, releases the SDA line and monitors the

line for an acknowledge. Once it receives this

acknowledge, the device will continue to transmit

data. If no acknowledge is sent by the Master, the

device terminates data transmission and waits for a

STOP condition.

WRITE OPERATIONS

Byte Write

In the Byte Write mode, the Master device sends the

START condition and the slave address information

(with the R/W

bit set to zero) to the Slave device. After

the Slave generates an acknowledge, the Master sends

a 8-bit address that is to be written into the address

pointers of the device. After receiving another acknow-

ledge from the Slave, the Master device transmits the

data to be written into the addressed memory location.

The device acknowledges once more and the Master

generates the STOP condition. At this time, the device

begins an internal programming cycle to non-volatile

memory. While the cycle is in progress, the device will

not respond to any request from the Master device.

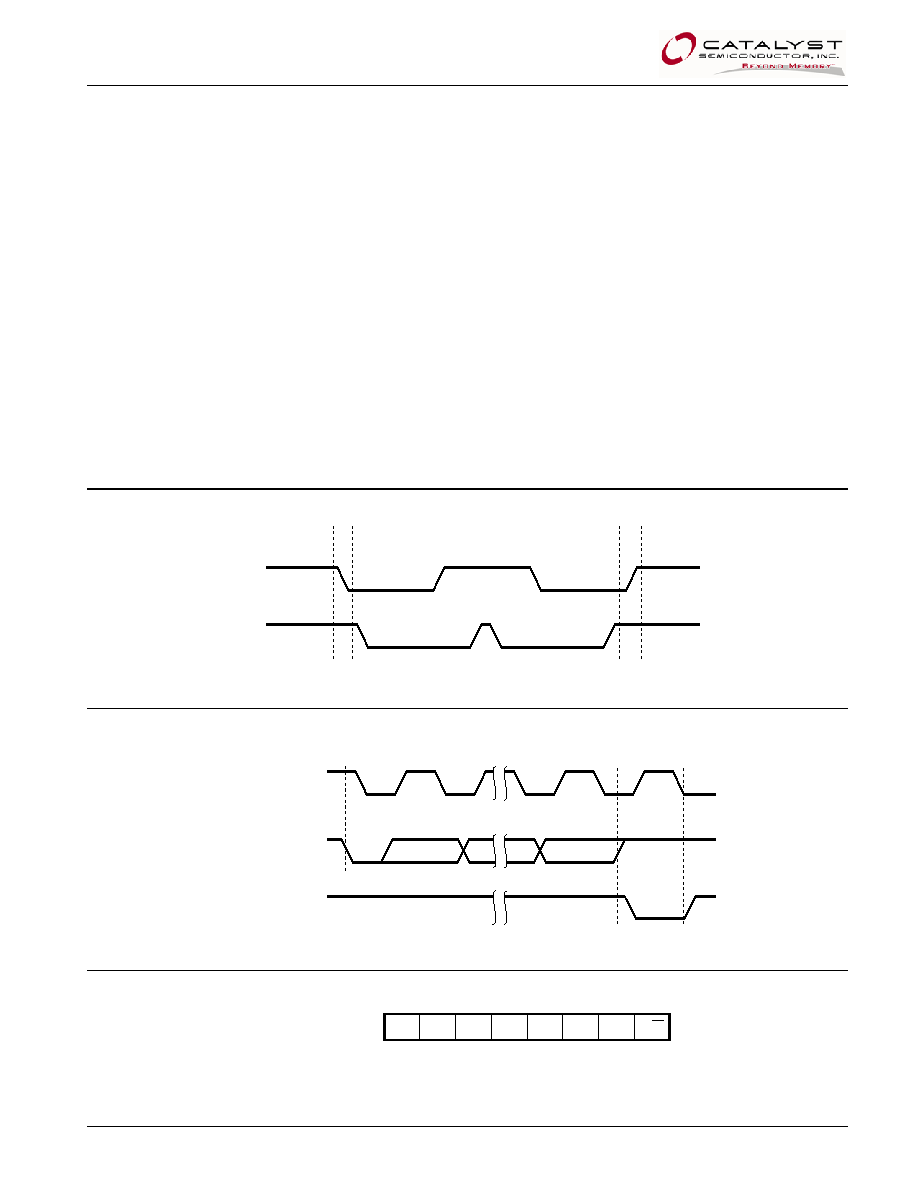

Figure 5. Start/Stop Timing

Figure 6. Acknowledge Timing

Figure 7: Slave Address Bits

START BIT

SDA

STOP BIT

SCL

ACKNOWLEDGE

1

START

SCL FROM

MASTER

89

DATA OUTPUT

FROM TRANSMITTER

DATA OUTPUT

FROM RECEIVER

1

01

0

R/W

Default Configuration

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CAT1320UI-28TE13 | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO8 |

| CAT1022WI45 | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO8 |

| CD-700KACGEB-35.328 | PHASE LOCKED LOOP, CQCC16 |

| CD-700KACGEB-51.840 | PHASE LOCKED LOOP, CQCC16 |

| CD-700KACGFB-24.576 | PHASE LOCKED LOOP, CQCC16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CAT1022WI-28-G | 功能描述:監(jiān)控電路 CPU w/2K RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| CAT1022WI-28-GT2 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

| CAT1022WI-28-GT3 | 功能描述:監(jiān)控電路 CPU SUP W/2K EEPROM RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| CAT1022WI-28T2 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

| CAT1022WI-28-T2 | 制造商:CATALYST 制造商全稱:Catalyst Semiconductor 功能描述:Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog Timer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。