- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298893 > BX80552651T (INTEL CORP) 32-BIT, 3400 MHz, MICROPROCESSOR, PBGA775 PDF資料下載

參數(shù)資料

| 型號: | BX80552651T |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 3400 MHz, MICROPROCESSOR, PBGA775 |

| 封裝: | FLIP CHIP, LGA-775 |

| 文件頁數(shù): | 81/108頁 |

| 文件大小: | 3283K |

| 代理商: | BX80552651T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁當(dāng)前第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

76

Datasheet

Land Listing and Signal Descriptions

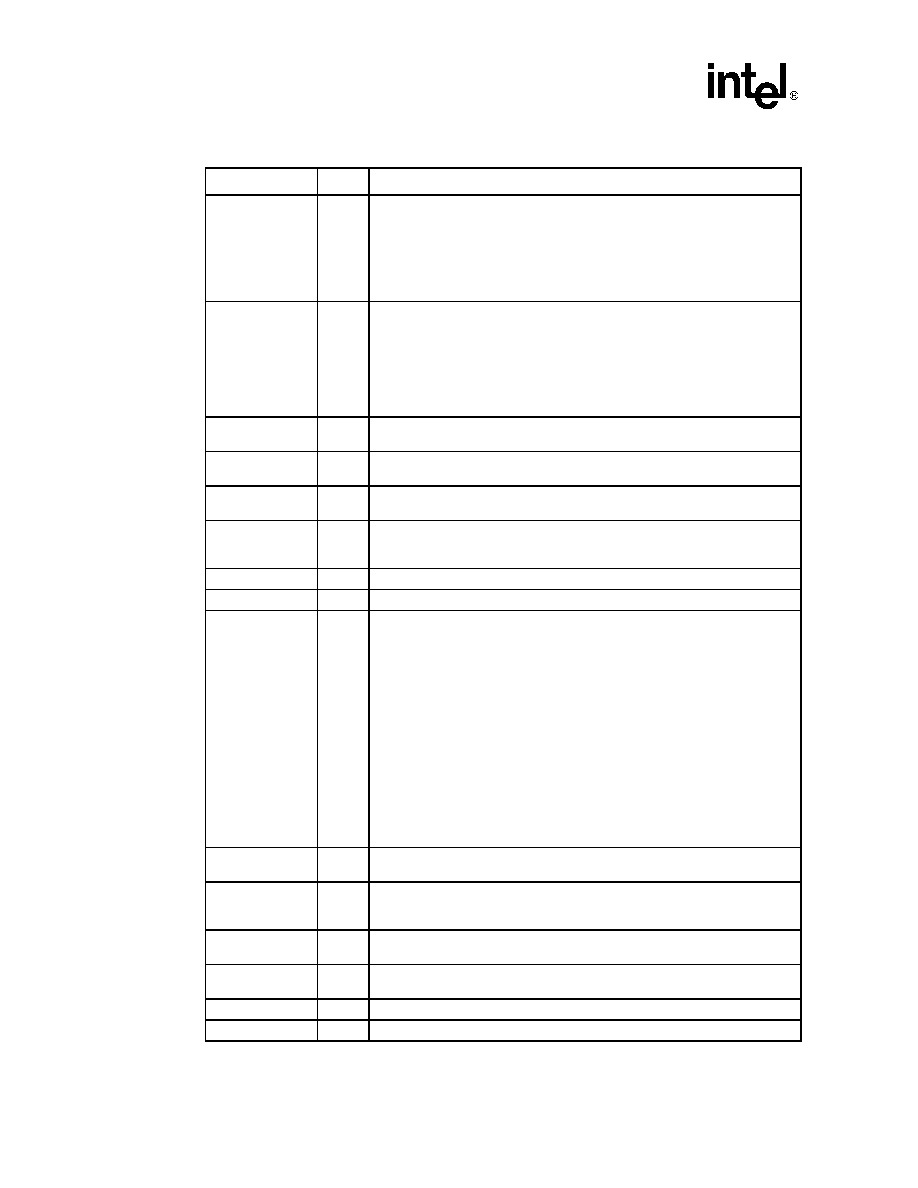

SMI#

Input

SMI# (System Management Interrupt) is asserted asynchronously by system

logic. On accepting a System Management Interrupt, the processor saves the

current state and enter System Management Mode (SMM). An SMI

Acknowledge transaction is issued, and the processor begins program

execution from the SMM handler.

If SMI# is asserted during the de-assertion of RESET#, the processor will tri-

state its outputs.

STPCLK#

Input

STPCLK# (Stop Clock), when asserted, causes the processor to enter a low

power Stop-Grant state. The processor issues a Stop-Grant Acknowledge

transaction, and stops providing internal clock signals to all processor core units

except the FSB and APIC units. The processor continues to snoop bus

transactions and service interrupts while in Stop-Grant state. When STPCLK# is

de-asserted, the processor restarts its internal clock to all units and resumes

execution. The assertion of STPCLK# has no effect on the bus clock; STPCLK#

is an asynchronous input.

TCK

Input

TCK (Test Clock) provides the clock input for the processor Test Bus (also

known as the Test Access Port).

TDI

Input

TDI (Test Data In) transfers serial test data into the processor. TDI provides the

serial input needed for JTAG specification support.

TDO

Output

TDO (Test Data Out) transfers serial test data out of the processor. TDO

provides the serial output needed for JTAG specification support.

TESTHI[13:0]

Input

TESTHI[13:0] must be connected to the processor’s appropriate power source

(refer to VTT_OUT_LEFT and VTT_OUT_RIGHT signal description) through a

resistor for proper processor operation. See Section 2.4 for more details.

THERMDA

Other

Thermal Diode Anode. See Section 5.2.7.

THERMDC

Other

Thermal Diode Cathode. See Section 5.2.7.

THERMTRIP#

Output

In the event of a catastrophic cooling failure, the processor will automatically

shut down when the silicon has reached a temperature approximately 20 °C

above the maximum T

C. Assertion of THERMTRIP# (Thermal Trip) indicates the

processor junction temperature has reached a level beyond where permanent

silicon damage may occur. Upon assertion of THERMTRIP#, the processor will

shut off its internal clocks (thus, halting program execution) in an attempt to

reduce the processor junction temperature. To protect the processor, its core

voltage (VCC) must be removed following the assertion of THERMTRIP#.

Driving of the THERMTRIP# signal is enabled within 10 s of the assertion of

PWRGOOD (provided VTTPWRGD, VTT, and VCC are asserted) and is

disabled on de-assertion of PWRGOOD (if VTTPWRGD, VTT, or VCC are not

valid, THERMTRIP# may also be disabled). Once activated, THERMTRIP#

remains latched until PWRGOOD, VTTPWRGD, VTT or VCC is de-asserted.

While the de-assertion of the PWRGOOD, VTTPWRGD, VTT or VCC signal will

de-assert THERMTRIP#, if the processor’s junction temperature remains at or

above the trip level, THERMTRIP# will again be asserted within 10 s of the

assertion of PWRGOOD (provided VTTPWRGD, VTT, and VCC are asserted).

TMS

Input

TMS (Test Mode Select) is a JTAG specification support signal used by debug

tools.

TRDY#

Input

TRDY# (Target Ready) is asserted by the target to indicate that it is ready to

receive a write or implicit writeback data transfer. TRDY# must connect the

appropriate pins/lands of all FSB agents.

TRST#

Input

TRST# (Test Reset) resets the Test Access Port (TAP) logic. TRST# must be

driven low during power on Reset.

VCC

Input

VCC are the power lands for the processor. The voltage supplied to these lands

is determined by the VID[5:0] pins.

VCCA

Input

VCCA provides isolated power for the internal processor core PLLs.

VCCIOPLL

Input

VCCIOPLL provides isolated power for internal processor FSB PLLs.

Table 4-3. Signal Description (Sheet 1 of 9)

Name

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BX80552661 | 32-BIT, 3600 MHz, MICROPROCESSOR, PBGA775 |

| BX80552651T2 | 32-BIT, 3400 MHz, MICROPROCESSOR, PBGA775 |

| BX80552641T | 32-BIT, 3200 MHz, MICROPROCESSOR, PBGA775 |

| BX80552641T2 | 32-BIT, 3200 MHz, MICROPROCESSOR, PBGA775 |

| BX805555060P | 64-BIT, MICROPROCESSOR, BGA771 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BX80552651T2 | 制造商:Intel 功能描述:P4 651 3.4GHZ LP-BTX 2MB - Boxed Product (Development Kits) |

| BX80552651T2 S L94W | 制造商:Intel 功能描述:MPU Pentium 制造商:Intel 功能描述:MPU Pentium? 4 Processor 651 65nm 3.4GHz 775-Pin FCLGA6 |

| BX80552651T2 S L9KE | 制造商:Intel 功能描述:MPU Pentium |

| BX80552661T2 | 制造商:Intel 功能描述:P4 661 3.6GHZ LP-BTX 2MB - Boxed Product (Development Kits) |

| BX80553915 S L9KB | 制造商:Intel 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。