- 您現(xiàn)在的位置:買賣IC網 > PDF目錄166624 > BUS-65142-470 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, QIP78 PDF資料下載

參數資料

| 型號: | BUS-65142-470 |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, QIP78 |

| 封裝: | KOVAR, QIP-78 |

| 文件頁數: | 8/26頁 |

| 文件大小: | 247K |

| 代理商: | BUS-65142-470 |

16

Data Device Corporation

www.ddc-web.com

BU-65142 and BUS-65142 SERIES

U-05/02-0

the appropriate I/O signals. Mode command illegalization and

handling are detailed below in TABLE 5.

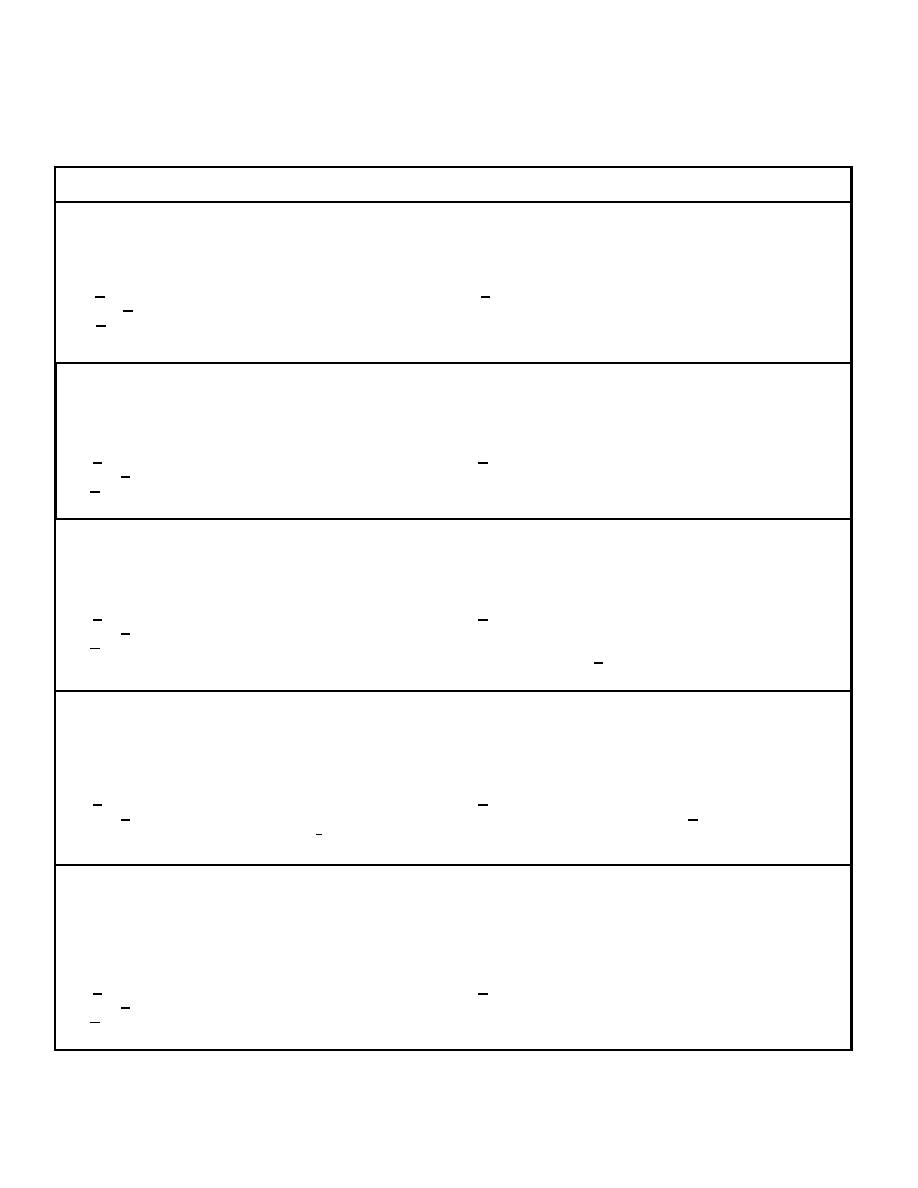

MODE CODES

The BUS-65142 implements all mode codes applicable to dual-

redundant systems. Mode codes can also be illegalized using

TABLE 5. MODE CODES IMPLEMENTED

DYNAMIC BUS CONTROL (00000)

MESSAGE SEQUENCE = DBC * STATUS

The RT responds with status. If the subsystem wants control of the bus, it must set DBACC in the Configuration Register.

ERROR CONDITIONS

1. Invalid Command. No response, command ignored.

2. Command Followed by Data Word. No status response. Bits Set: message error (SW), High Word Count (BIT Word).

3. T/R bit Set to Zero. No status response. Bits set: message error (S/W), T/R Error (BIT Word).

4. Zero T/R bit and Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code,

T/R Error (BIT Word).

5. Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code (BIT Word).

SYNCHRONIZE WITHOUT DATA WORD (00001)

MESSAGE SEQUENCE = SYNC * STATUS

The RT responds with status. If sent as a broadcast, the broadcast receive bit will be set and status response suppressed.

ERROR CONDITIONS

1. Invalid Command. No response, command ignored.

2. Command Followed by Data Word. No status response. Bits Set: message error (SW), High Word Count (BIT Word)

3. T/R bit Set to Zero. No status response. Bits set: message error (S/W), T/R Error (BIT Word).

4. Zero T/R bit and Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code,

T/R Error (BIT Word).

STATUS WORD (00010)

MESSAGE SEQUENCE = TRANSMIT WORD * STATUS

The status and BIT word registers are not altered by this command and contain the status from the previous command.

ERROR CONDITIONS

1. Invalid Command. No response, command ignored.

2. Command Followed by Data Word. No status response. Bits Set: message error (SW), High Word Count (BIT Word)

3. T/R bit Set to Zero. No status response. Bits set: message error (S/W), T/R Error (BIT Word).

4. Zero T/R bit and Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code,

T/R Error (BIT Word).

5. Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), T/R Error (BIT Word).

INITIATE SELF-TEST (00011)

MESSAGE SEQUENCE = SELF TEST * STATUS

The RT responds with a status word. If the command was broadcast, the broadcast received bit is set and status transmission suppressed.

Short-loop test is initiated on the status word transmitted. If the test fails, an RT fail flag is set.

ERROR CONDITIONS

1. Invalid Command. No response, command ignored.

2. Command Followed by Data Word. No status response. Bits Set: message error (SW), High Word Count (BIT Word)

3. T/R bit Set to Zero. No status response. Bits set: message error (S/W), T/R Error (BIT Word).

4. Zero T/R bit and Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), T/R Error (BIT Word).

5. Fault Test. Bits set: terminal flag (S/W),

Loop Test Fail, Current 1553 Bus (A or B) Loop Test Fail (BIT Word)

B

/

A

TRANSMITTER SHUTDOWN (00100)

MESSAGE SEQUENCE =SHUTDOWN * STATUS

This command is only used with dual redundant bus systems. The RT responds with status. At the end of the status transmission, the RT inhibits

any further transmission from the dual redundant channel. Once shutdown, the transmitter can only be reactivated by OVERRIDE TRANSMITTER

SHUTDOWN or RESET RT commands.

ERROR CONDITIONS

1. Invalid Command. No response, command ignored.

2. Command Followed by Data Word. No status response. Bits Set: message error (SW), High Word Count (BIT Word)

3. T/R bit Set to Zero. No status response. Bits set: message error (S/W), T/R Error (BIT Word).

4. Zero T/R bit and Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code,

T/R Error (BIT Word).

* = Status Response Time

相關PDF資料 |

PDF描述 |

|---|---|

| BUS-65142-550K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, QIP78 |

| BUS-65142-590K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, QIP78 |

| BUS-65143-250Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, QIP78 |

| BUS-65143-470L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, QIP78 |

| BUS-65143-480Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, QIP78 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| BU-S802 | 制造商:Fuji Electric 功能描述: |

| BU-S803 | 制造商:Fuji Electric 功能描述: |

| BUS98 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:SITCHMODE Series NPN Silicon Power Transistors |

| BUS98/D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SWITCHMODE? Series NPN Silicon Power Transistors |

| BUS98A | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:SITCHMODE Series NPN Silicon Power Transistors |

發(fā)布緊急采購,3分鐘左右您將得到回復。