- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄256043 > BU-62743F4-110Y (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 PDF資料下載

參數(shù)資料

| 型號(hào): | BU-62743F4-110Y |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| 封裝: | 1 INCH, CERAMIC, QFP-72 |

| 文件頁數(shù): | 7/99頁 |

| 文件大小: | 578K |

| 代理商: | BU-62743F4-110Y |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

Data Device Corporation

62743_pre7_noSA-DB.DOC

www.ddc-web.com

8-07-02

15

PCI Status register This register records status information for PCI bus related

events. Reads to this register behave normally, but writes can only reset bits. A

bit is reset whenever the register is written and the data in the corresponding bit

location is a 1.

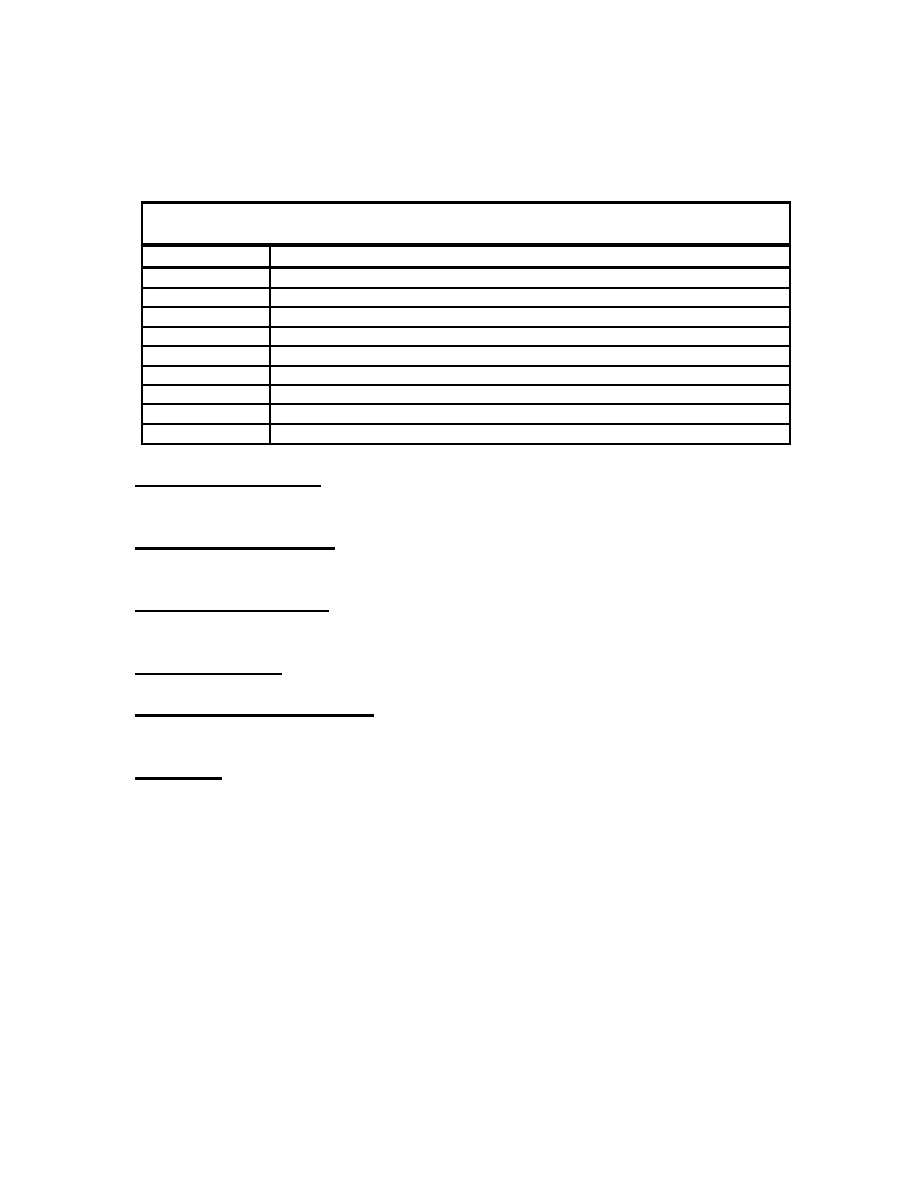

Table 6. PCI Status Register

BIT

DESCRIPTION

31

Detected Parity Error

30

Signaled System Error

29:28

0

27

Signaled Target Abort

26:25

DEVSEL# Timing = 01 (medium)

24

0

23

Fast Back-to-Back Capable = 1

22:21

0

20:16

Reserved, 0s

Detected Parity Error: This bit will be set by the device whenever it detects a

parity error, even if the Parity Error Control bit in the PCI Control register is 0b.

Signaled System Error: This bit indicates when the device has asserted

SERR#. The value after RST# is 0b.

Signaled Target Abort: This bit is set whenever the device terminates a

transaction with a Target-Abort. The value after RST# is 0b.

DEVSEL# Timing: The PCI enhanced mini-ACE is 01b, medium.

Fast Back-to-Back Capable: This bit is set to 1b and indicates that the device is

capable of accepting fast back-to-back transactions.

Reserved: These bits are read-only and return zeroes when read.

Subsystem Vendor ID/Subsystem Device ID field is an alias of the Vendor

ID/Device ID fields in Configuration Register 00h.

Base Address Registers are used to implement ACE memory space (BAR0)

and ACE register space (BAR1). Base Address Registers 2 through 5 are not

used.

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。