- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄256245 > BU-61845G4-120Z (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 PDF資料下載

參數(shù)資料

| 型號: | BU-61845G4-120Z |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| 封裝: | 25.40 X 25.40 MM, 2.54 MM HEIGHT, CERAMIC, QFP-72 |

| 文件頁數(shù): | 16/60頁 |

| 文件大小: | 457K |

| 代理商: | BU-61845G4-120Z |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

23

Data Device Corporation

www.ddc-web.com

BU-6174X/6184X/6186X

F-10/02-300

REMOTE TERMINAL (RT) ARCHITECTURE

The Enhanced Mini-ACE/-ACE's RT architecture builds upon

that of the ACE and Mini-ACE. The Enhanced Mini-ACE/-ACE

provides multiprotocol support, with full compliance to all of the

commonly used data bus standards, including MIL-STD-1553A,

MIL-STD-1553B Notice 2, STANAG 3838, General Dynamics

16PP303, and McAirA3818, A5232, and A5690. For the

Enhanced Mini-ACE/-ACE RT mode, there is programmable

flexibility enabling the RT to be configured to fulfill any set of sys-

tem requirements. This includes the capability to meet the MIL-

STD-1553A response time requirement of 2 to 5 s, and multiple

options for mode code subaddresses, mode codes, RT status

word, and RT BIT word.

The Enhanced Mini-ACE/-ACE RT protocol design implements

all of the MIL-STD-1553B message formats and dual redundant

mode codes. The design has passed validation testing for MIL-

STD-1553B compliance. The Enhanced Mini-ACE/-ACE RT per-

forms comprehensive error checking including word and format

validation, and checks for various RT-to-RT transfer errors. One of

the main features of the Enhanced Mini-ACE/-ACE RT is its

choice of memory management options. These include single

buffering by subaddress, double buffering for individual receive

subaddresses, circular buffering by individual subaddresses, and

global circular buffering for multiple (or all) subaddresses.

Other features of the Enhanced Mini-ACE/-ACE RT include a

set of interrupt conditions, a flexible status queue with filtering

based on valid and/or invalid messages, flexible command ille-

galization, programmable busy by subaddress, multiple options

on time tagging, and an "auto-boot" feature which allows the RT

to initialize as an online RT with the busy bit set following power

turn-on.

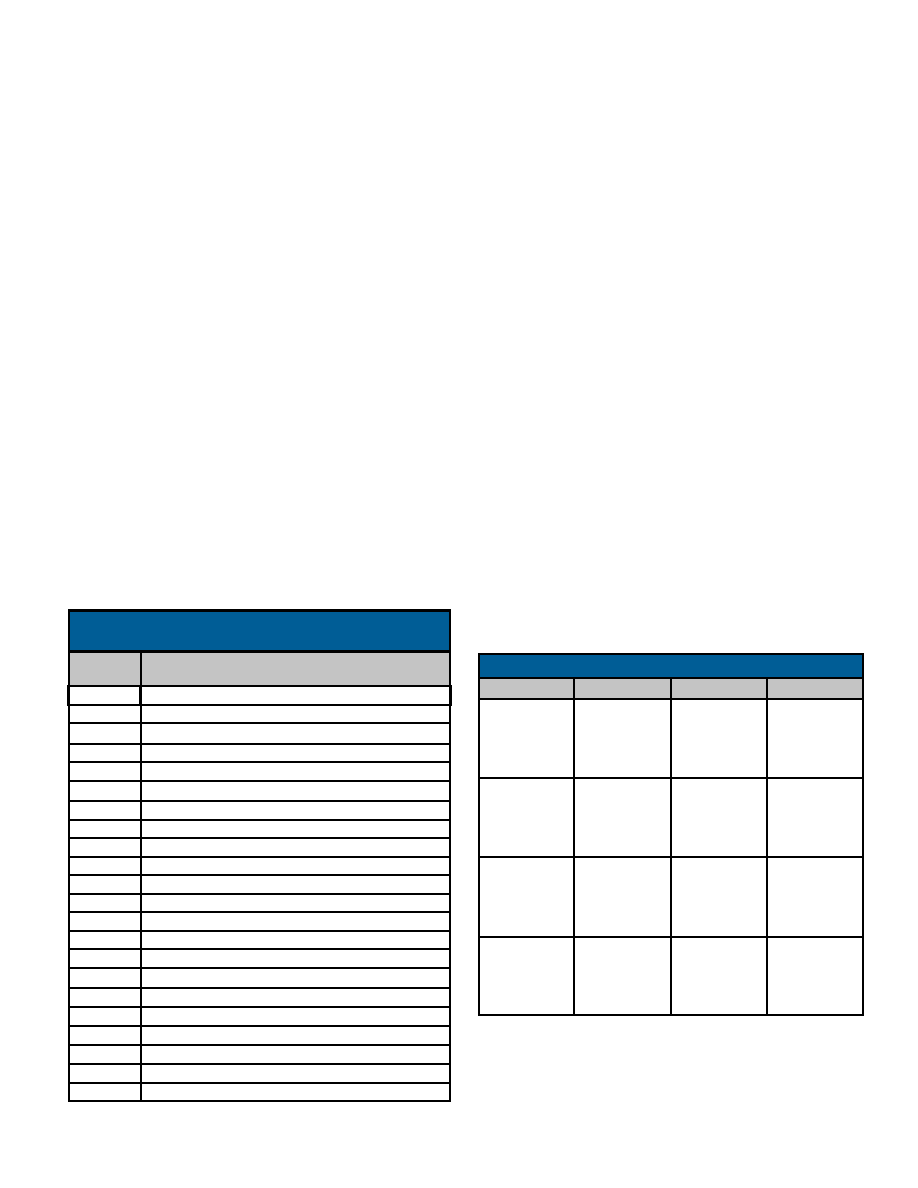

RT MEMORY ORGANIZATION

TABLE 38 illustrates a typical memory map for an Enhanced Mini-

ACE/-ACE RT with 4K RAM. The two Stack Pointers reside in

fixed locations in the shared RAM address space: address 0100

(hex) for the Area A Stack Pointer and address 0104 for the Area

B Stack Pointer. In addition to the Stack Pointer, there are sever-

al other areas of the shared RAM address space that are desig-

nated as fixed locations (all shown in bold). These are for the

Area A and Area B lookup tables, the illegalization lookup table,

the busy lookup table, and the mode code data tables.

The RT lookup tables (reference TABLE 39) provide a mecha-

nism for allocating data blocks for individual transmit, receive, or

broadcast subaddresses. The RT lookup tables include subad-

dress control words as well as the individual data block pointers.

If command illegalization is used, address range 0300-03FF is

used for command illegalizing. The descriptor stack RAM area, as

well as the individual data blocks, may be located in any of the

non-fixed areas in the shared RAM address space.

Note that in TABLE 38, there is no area allocated for "Stack B".

This is shown for purpose of simplicity of illustration. Also, note

that in TABLE 38, the allocated area for the RT command stack is

256 words. However, larger stack sizes are possible. That is, the

RT command stack size may be programmed for 256 words (64

messages), 512, 1024, or 2048 words (512 messages) by means

of bits 14 and 13 of Configuration Register 3.

Data Block 100

0FE0-0FFF

Data Block 6

0420-043F

Data Block 5

0400-041F

Command Illegalizing Table

0300-03FF

RESERVED

Data Block 1-4

0280-02FF

Data Block 0

0260-027F

(not used)

0248-025F

Busy Bit Lookup Table

0240-0247

Lookup Table B

01C0-023F

Lookup Table A

0140-01BF

Mode Code Data

0110-013F

Mode Code Selective Interrupt Table

0108-010F

Global Circular Buffer B Pointer

Stack Pointer B

0105

0104

RESERVED

0102-0103

Global Circular Buffer A Pointer

Stack Pointer A

0101

0100

Stack A

0000-00FF

DESCRIPTION

ADDRESS

(HEX)

0106-0107

TABLE 38. TYPICAL RT MEMORY MAP (SHOWN

FOR 4K RAM)

Subaddress

Control Word

Lookup Table

(Optional)

SACW SA0

SACW SA31

0220

023F

01A0

01BF

Broadcast

Lookup Pointer

Table

(Optional)

Bcst SA0

Bcst SA31

0200

021F

0180

019F

Transmit

Lookup Pointer

Table

Tx SA0

Tx SA31

01E0

01FF

0160

017F

Receive

(/Broadcast)

Lookup Pointer

Table

Rx(/Bcst) SA0

Rx(/Bcst) SA31

01C0

01DF

0140

015F

COMMENT

DESCRIPTION

AREA B

AREA A

TABLE 39. RT LOOK-UP TABLES

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61845G4-150L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61845G4-160S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61845G4-172K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61845G4-192 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, MQFP72 |

| BU-61864F3-140K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61860B3NEW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |μ-ACE (Micro-ACE?) |

| BU-61864 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MIL-STD-1553 Components |Enhanced Mini-ACE? |

| BU-61864F3-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864F3-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU-61864F4-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。