- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄210366 > BU-61582D1-391Q (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 PDF資料下載

參數(shù)資料

| 型號(hào): | BU-61582D1-391Q |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| 封裝: | CERAMIC, DIP-70 |

| 文件頁(yè)數(shù): | 19/48頁(yè) |

| 文件大小: | 378K |

| 代理商: | BU-61582D1-391Q |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

26

Data Device Corporation

www.ddc-web.com

BU-61582

G-08/02-250

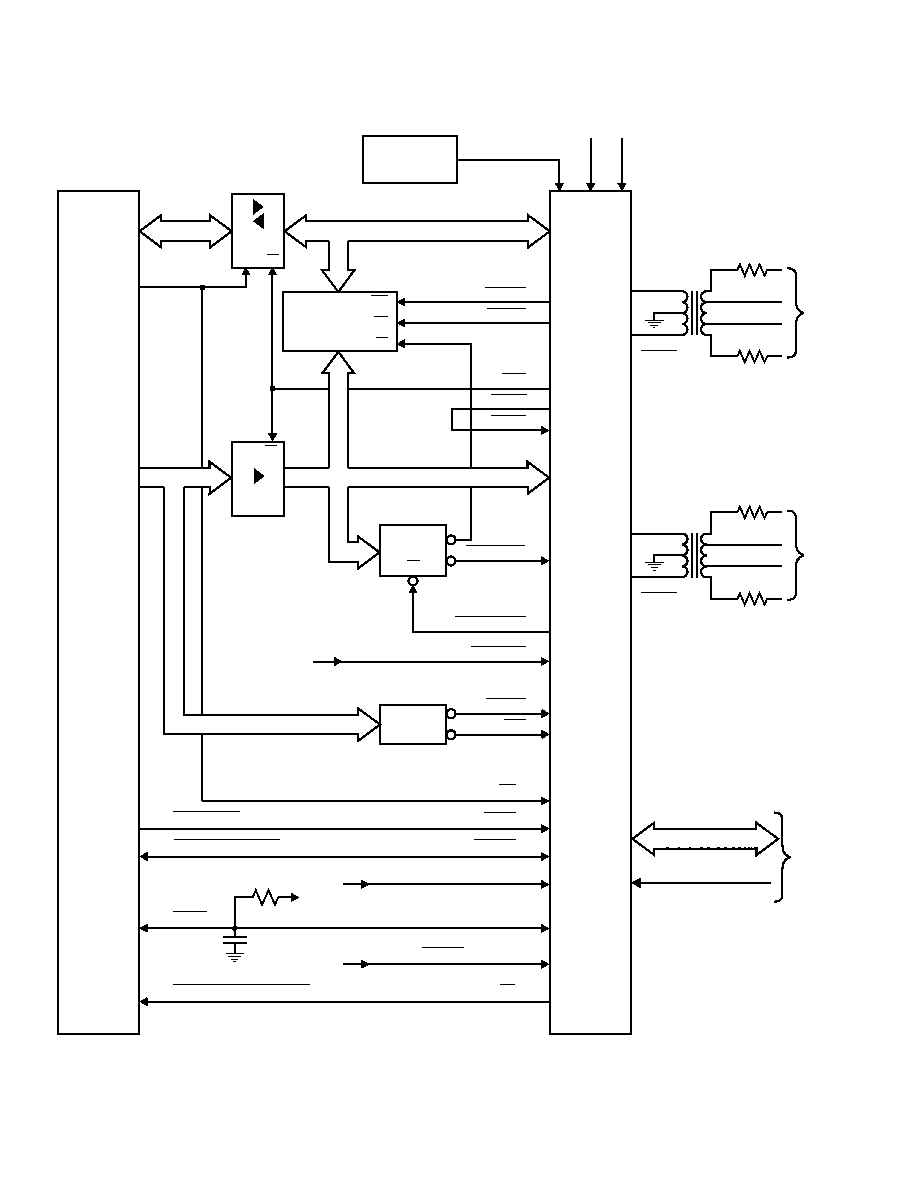

HOST

SP'ACE

55

55

8

7

5

4

1

2

3

CH. A

TX/RXA

55

55

8

7

5

4

1

2

3

CH. B

TX/RXB

RTAD4-RTAD0

RT

ADDRESS,

PARITY

RTADP

D15-D0

+5V

-12V/-15V

CLK IN

16 MHz

CLOCK

OSCILLATOR

RD/WR

STRBD

READYD

TAG_CLK

CPU STROBE

CPU ACKNOWLEDGE

RESET

+5V

MSTCLR

SSFLAG/EXT_TRIG

INT

CPU INTERRUPT REQUEST

'245

DIR

EN

CPU D15-D0

RAM

64K x 16 MAX

WR

OE

CS

MEMWR

MEMOE

IOEN

DTREQ

DTGRT

'244

EN

ADDRESS

DECODER

EN

ADDRESS

DECODER

MEMENA-IN

A15-A0

CPU A15-A0

MEMENA-OUT

SELECT

MEM/REG

TRANSPARENT/BUFFERED

FIGURE 10. 16-BIT TRANSPARENT MODE

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。