- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄298850 > BCM5714C PCI BUS CONTROLLER, PBGA484 PDF資料下載

參數(shù)資料

| 型號(hào): | BCM5714C |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA484 |

| 封裝: | PLASTIC, BGA-484 |

| 文件頁(yè)數(shù): | 2/2頁(yè) |

| 文件大?。?/td> | 171K |

| 代理商: | BCM5714C |

O V ERVI EW

Phone: 949-926-5000

Fax: 949-926-5203

E-mail: info@broadcom.com

Web: www.broadcom.com

BROADCOM CORPORATION

5300 California Avenue

Irvine, California 92617

2009 by BROADCOM CORPORATION. All rights reserved.

5714C-PB03-R

04/15/09

Broadcom, the pulse logo, Connecting everything, the Connecting everything logo, NetXtreme,

and Smart Load Balancing are among the trademarks of Broadcom Corporation and/or its affiliates in

the United States, certain other countries and/or the EU. Any other trademarks or trade names mentioned

are the property of their respective owners.

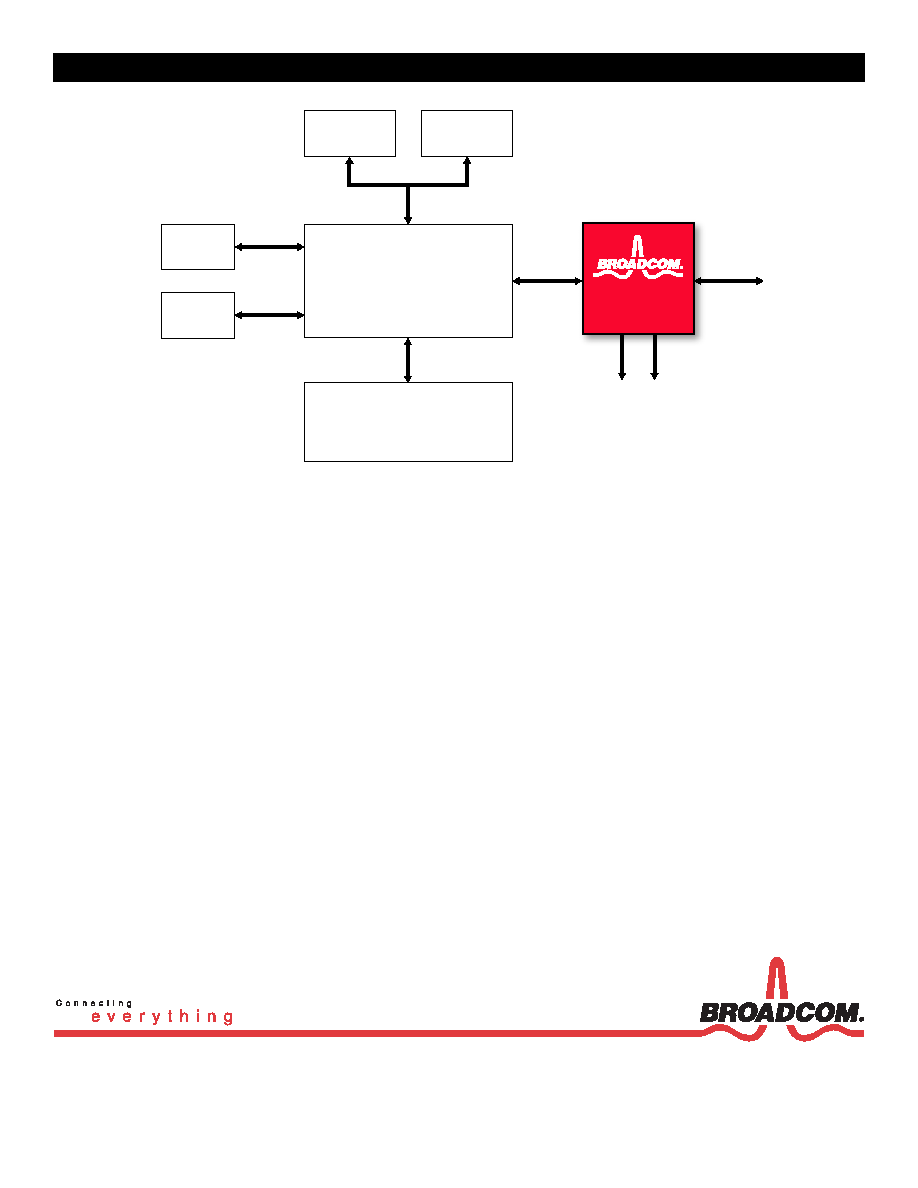

System Block Diagram

The BCM5714C device is a highly integrated communication and

storage bridge for entry-level servers and embedded applications. The

primary applications of the BCM5714C are UP and DP servers featuring

PCI Express connectivity for I/O expansion.

The BCM5714C provides these key features:

Dual gigabit NIC ports (MAC and PHY)

One full 64-bit/133 MHz PCI-X 1.0 bus

Host interface of PCI Express

The BCM5714C connects to server chip sets with an x4 PCI Express

interface and provides an independent PCI-X 1.0 bus for peripheral

connectivity. The x4 PCI Express interface is a flexible design and

supports x1 and x2 PCI Express connectivity as well. The PCI-X bus is

64 bits wide and runs at 133 MHz.

As an integrated I/O bridge that provides a high-performance data flow

path between the PCI Express host interface and the integrated I/O

subsystem, the PCI-X bus provides high-performance I/O expansion

within the system, while the Gigabit Ethernet interfaces provide high

performance network interfaces to the external world. The 64-bit PCI-X

bus segment operates at 33 MHz, 66 MHz, 100 MHz, and 133 MHz. The

GbE interface represents the fourth generation of Broadcom server

controllers with fully integrated copper transceivers.

The features of the PCI-X bridge include the following:

Allow concurrency between the PCI Express and the PCI-X buses

Eight-deep PCI Express-to-PCI-X memory write posting (PCI

Express-to-PCI-X transactions)

Four-deep PCI Express-to-PCI-X non-posted request queue (PCI

Express-to-PCI-X transactions)

Caching with a 16-deep, 32-byte I/O cache for PCI-to-main memory

transactions for each PCI bus

Support write-through caching protocol

Support up to 14 outstanding split transactions (PCI-X-to-main

memory transactions)

Eight-deep PCI-X-to-PCI Express request queue (PCI-X-to-main

memory transactions)

Parity protection on the PCI-X bus in a conventional PCI and PCI-X

mode1

Optional ECC protection on the PCI-X bus in PCI-X mode1

Three programmable regions each for PCI-X memory and one region

for I/O

VGA-compatible addressing support

Multiple I/O APIC support

Peer-to-peer transfer support

Integrated PCI-X bus arbitration that supports up to four PCI-X bus

masters

PCI-X bus error reporting

RAS features

BCM5714C

DDR

Processor

DDR

Memory Controller

Southbridge

PCI

Express

PCI-X

Dual GbE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BCM5802 | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP144 |

| BCW34 | Bipolar NPN Device |

| BCY59C | Bipolar NPN Device in A Hermetically sealed TO18 Metal Package |

| BCY78CDWP | 32 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

| BCY78BDWP | 32 V, PNP, Si, SMALL SIGNAL TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BCM5714CKPB | 功能描述:PCIE PCIX BRIDGE DUAL 制造商:broadcom limited 系列:* 零件狀態(tài):最後搶購(gòu) 標(biāo)準(zhǔn)包裝:280 |

| BCM5714CKPBG | 功能描述:DUAL GIG ETH CNTLR+INT PCE-E-P 制造商:broadcom limited 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:40 |

| BCM5714CKPBGG | 功能描述:PCIE PCIX BRIDGE DUAL 制造商:broadcom limited 系列:* 零件狀態(tài):最後搶購(gòu) 標(biāo)準(zhǔn)包裝:1 |

| BCM5715CKPB | 功能描述:PCI-EXPRESS 2-PORT GBE 制造商:broadcom limited 系列:* 零件狀態(tài):最後搶購(gòu) 標(biāo)準(zhǔn)包裝:280 |

| BCM5715CKPBG | 功能描述:PCI-EXPRESS DUAL PORT GBE CONT 制造商:broadcom limited 系列:* 零件狀態(tài):最後搶購(gòu) 標(biāo)準(zhǔn)包裝:40 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。