- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄352484 > ATMEGA329P (Atmel Corp.) -bit AVR Microcontroller with 8K Bytes In- System Programmable Flash PDF資料下載

參數(shù)資料

| 型號(hào): | ATMEGA329P |

| 廠商: | Atmel Corp. |

| 元件分類: | 8位微控制器 |

| 英文描述: | -bit AVR Microcontroller with 8K Bytes In- System Programmable Flash |

| 中文描述: | 位AVR微控制器具有8K字節(jié)的系統(tǒng)內(nèi)可編程閃存 |

| 文件頁(yè)數(shù): | 83/83頁(yè) |

| 文件大?。?/td> | 8336K |

| 代理商: | ATMEGA329P |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)當(dāng)前第83頁(yè)

94

7707F–AVR–11/10

AT90USB82/162

generation. Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is

down-counting.

The setup of the OC0x should be performed before setting the Data Direction Register for the

port pin to output. The easiest way of setting the OC0x value is to use the Force Output Com-

pare (FOC0x) strobe bits in Normal mode. The OC0x Registers keep their values even when

changing between Waveform Generation modes.

Be aware that the COM0x1:0 bits are not double buffered together with the compare value.

Changing the COM0x1:0 bits will take effect immediately.

14.5

Compare Match Output Unit

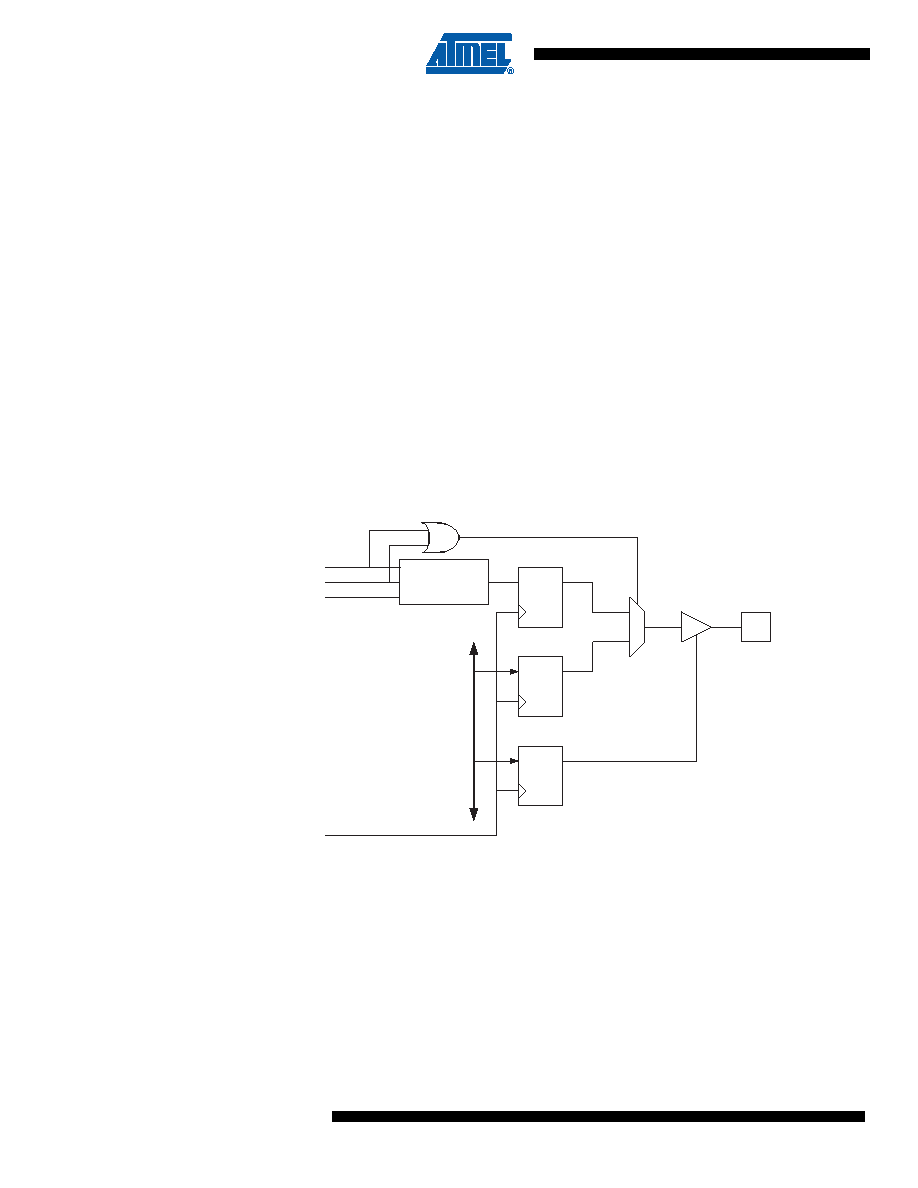

The Compare Output mode (COM0x1:0) bits have two functions. The Waveform Generator uses

the COM0x1:0 bits for defining the Output Compare (OC0x) state at the next Compare Match.

Also, the COM0x1:0 bits control the OC0x pin output source. Figure 14-4 shows a simplified

schematic of the logic affected by the COM0x1:0 bit setting. The I/O Registers, I/O bits, and I/O

pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers

(DDR and PORT) that are affected by the COM0x1:0 bits are shown. When referring to the

OC0x state, the reference is for the internal OC0x Register, not the OC0x pin. If a system reset

occur, the OC0x Register is reset to “0”.

Figure 14-4. Compare Match Output Unit, Schematic

The general I/O port function is overridden by the Output Compare (OC0x) from the Waveform

Generator if either of the COM0x1:0 bits are set. However, the OC0x pin direction (input or out-

put) is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction

Register bit for the OC0x pin (DDR_OC0x) must be set as output before the OC0x value is visi-

ble on the pin. The port override function is independent of the Waveform Generation mode.

The design of the Output Compare pin logic allows initialization of the OC0x state before the out-

put is enabled. Note that some COM0x1:0 bit settings are reserved for certain modes of

PORT

DDR

DQ

OCnx

Pin

OCnx

DQ

Waveform

Generator

COMnx1

COMnx0

0

1

D

ATA

B

U

S

FOCn

clk

I/O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ATMEGA324P | -bit AVR Microcontroller with 8K Bytes In- System Programmable Flash |

| ATMEGA644P | -bit AVR Microcontroller with 8K Bytes In- System Programmable Flash |

| ATMEGA3250P | -bit AVR Microcontroller with 8K Bytes In- System Programmable Flash |

| ATMEGA325P | -bit AVR Microcontroller with 8K Bytes In- System Programmable Flash |

| ATTINY24 | 8-bit Microcontroller with 2/4/8K Bytes In-System Programmable Flash |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ATMEGA329P_06 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit Microcontroller with 32K Bytes In-System Programmable Flash |

| ATMEGA329P_07 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit Microcontroller with 32K Bytes In-System Programmable Flash |

| ATMEGA329P_08 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit Microcontroller with 32K Bytes In-System Programmable Flash |

| ATMEGA329P_09 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit Microcontroller with 32K Bytes In-System Programmable Flash |

| ATMEGA329P_1 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8-bit Microcontroller with 32K Bytes In-System Programmable Flash |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。