- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4184 > AT6005-4JC (Atmel)IC FPGA 15K GATE 4NS 84PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | AT6005-4JC |

| 廠商: | Atmel |

| 文件頁(yè)數(shù): | 2/28頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 15K GATE 4NS 84PLCC |

| 標(biāo)準(zhǔn)包裝: | 16 |

| 系列: | AT6000(LV) |

| 邏輯元件/單元數(shù): | 3136 |

| 輸入/輸出數(shù): | 64 |

| 門(mén)數(shù): | 15000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 84-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 84-PLCC(29.31x29.31) |

| 其它名稱: | AT60054JC |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

AT6000(LV) Series

10

memory to configure the FPGA. Addresses change after

the rising edge of the CCLK signal.

CSOUT or I/O

When cascading devices, CSOUT is an output used to

enable other devices. CSOUT should be connected to the

CS input of the downstream device. The CSOUT function is

optional and can be disabled during initial programming

when cascading is not used. When cascading devices,

CSOUT should be dedicated to configuration and not used

as a configurable I/O.

CHECK or I/O

During configuration, CHECK is a TTL input that can be

used to enable the data check function at the beginning of

a configuration cycle. No data is written to the device while

CHECK is low. Instead, the configuration file being applied

to D0 (or D0 - D7, in parallel mode) is compared with the

current contents of the internal configuration RAM. If a mis-

match is detected between the data being loaded and the

data already in the RAM, the ERR pin goes low. The

CHECK function is optional and can be disabled during ini-

tial programming.

ERR or I/O

During configuration, ERR is an output. When the CHECK

function is activated and a mismatch is detected between

the current configuration data stream and the data already

loaded in the configuration RAM, ERR goes low. The ERR

ouput is a registered signal. Once a mismatch is found, the

signal is set and is only reset after the configuration cycle is

restarted. ERR is also asserted for configuration file errors.

The ERR function is optional and can be disabled during

initial programming.

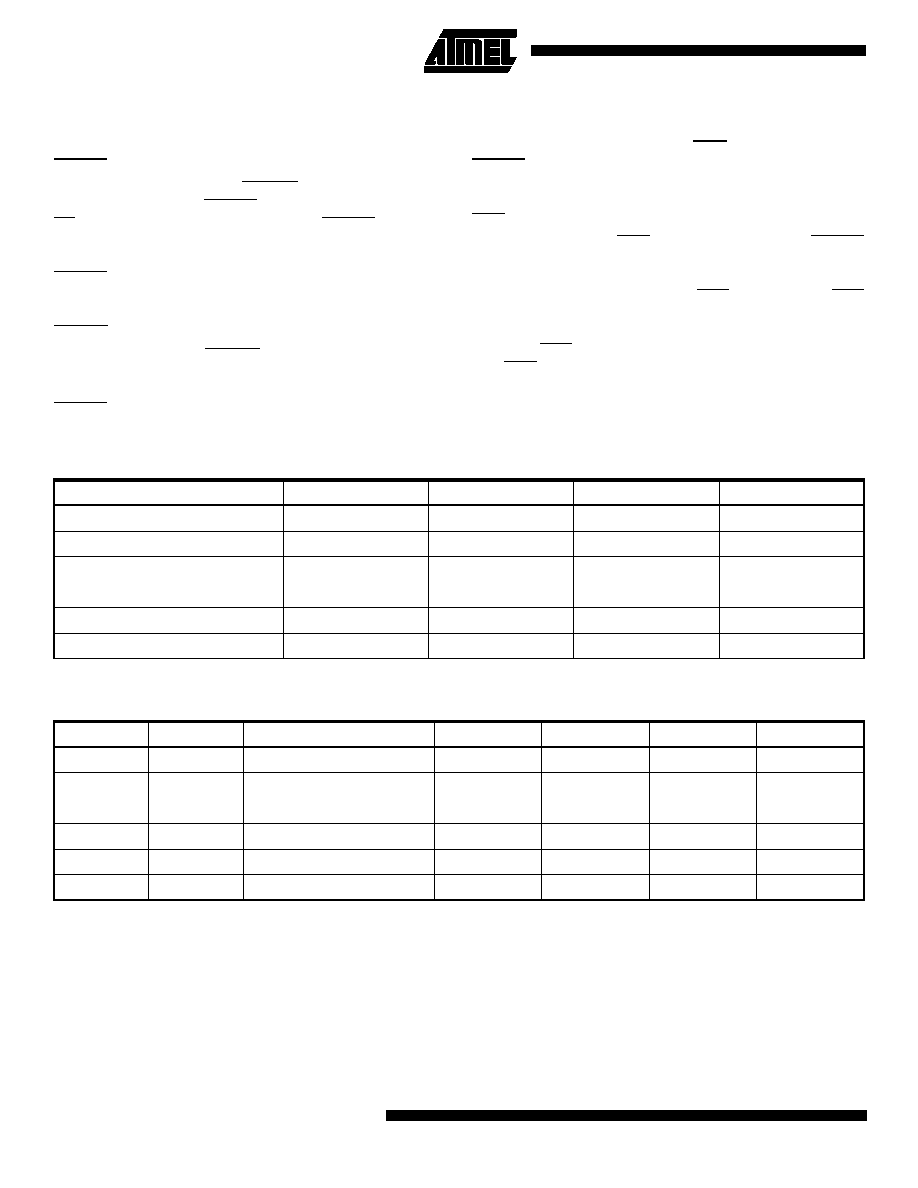

Device Pinout Selection (Max. Number of User I/O)

AT6002

AT6003

AT6005

AT6010

84 PLCC

64 I/O

-

100 VQFP

80 I/O

-

132 PQFP

96 I/O

108 I/O

144 TQFP

95 I/O

120 I/O

108 I/O

120 I/O

208 PQFP

-

172 I/O

240 PQFP

-

204 I/O

Bit-stream Sizes

Mode(s)

Type

Beginning Sequence

AT6002

AT6003

AT6005

AT6010

1

Parallel

Preamble

2677

4153

8077

16393

2

Parallel

Preamble

2677

4153

8077

16393

3

Serial

Null Byte/Preamble

2678

4154

8078

16394

4

Serial

Null Byte/Preamble

2678

4154

8078

16394

5

Parallel

Preamble

2677

4153

8077

16393

6

Parallel

Preamble/Preamble

2678

4154

8078

16394

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AT6005-4AI | IC FPGA 15K GATE 4NS 100VQFP |

| AT6003-2JC | IC FPGA 9K GATE 2NS 84PLCC |

| AT6003-2AI | IC FPGA 2NS 100VQFP |

| AT6003-2AC | IC FPGA 9K GATE 2NS 100VQFP |

| ACC65DREN-S93 | CONN EDGECARD 130PS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT6005-4JI | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 15K GATE 4NS IND TEMP RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| AT6005-4QC | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 15K GATE 4NS COM TEMP RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| AT6005-4QI | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 15K GATE 4NS IND TEMP RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| AT6005-4UC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| AT6005-4UI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。