- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295111 > AT40K40LV-3BGC (ATMEL CORP) FPGA, 2304 CLBS, 40000 GATES, PBGA352 PDF資料下載

參數(shù)資料

| 型號: | AT40K40LV-3BGC |

| 廠商: | ATMEL CORP |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 2304 CLBS, 40000 GATES, PBGA352 |

| 封裝: | BGA-352 |

| 文件頁數(shù): | 21/67頁 |

| 文件大小: | 1589K |

| 代理商: | AT40K40LV-3BGC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁

28

AT40K/AT40KLV Series FPGA

0896C–FPGA–04/02

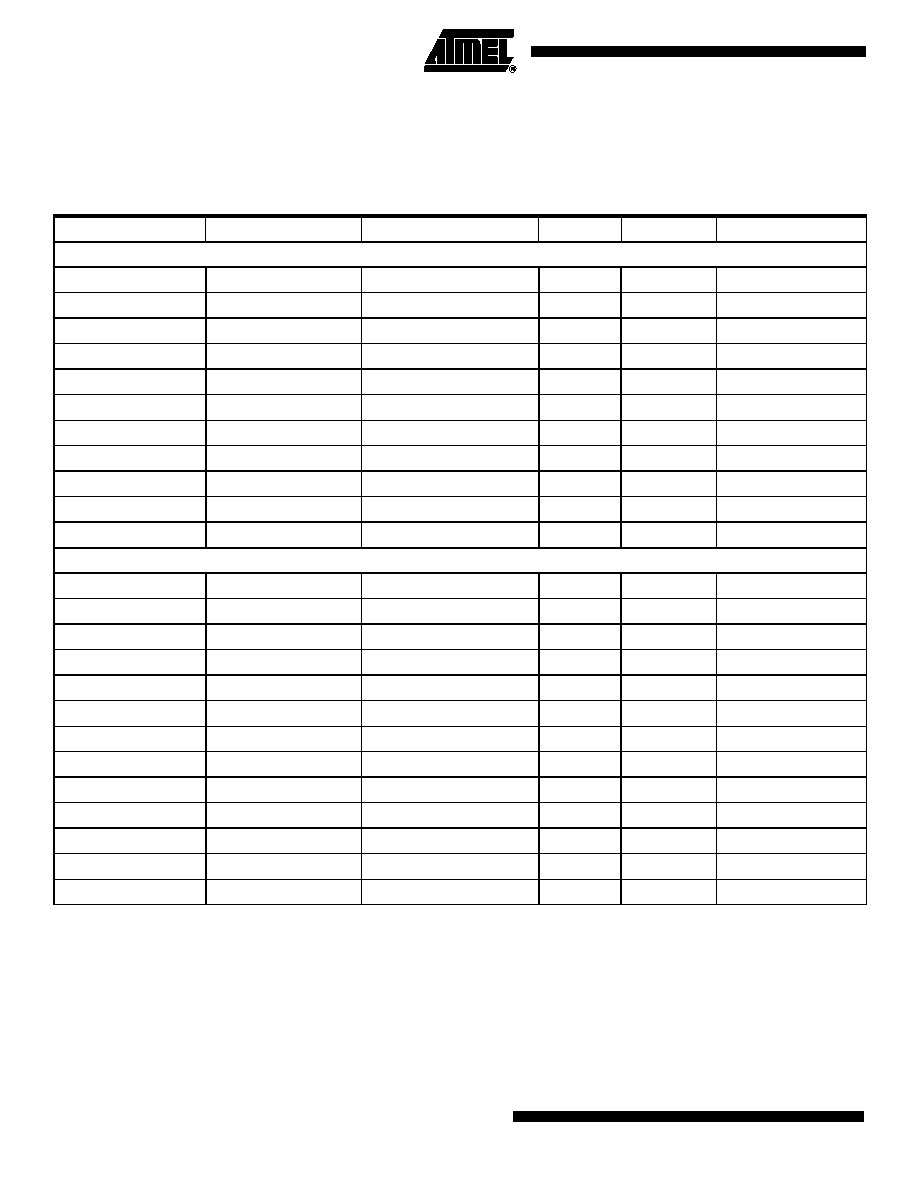

AC Timing Characteristics – 5V Operation AT40K

Delays are based on fixed loads and are described in the notes.

Maximum times based on worst case: VCC = 4.75V, temperature = 70°C

Minimum times based on best case: VCC = 5.25V, temperature = 0°C

Maximum delays are the average of tPDLH and tPDHL.

Cell Function

Parameter

Path

-2

Units

Notes

Async RAM

Write

tWECYC (Minimum)

cycle time

8.0

ns

Write

t

WEL (Minimum)

we

3.0

ns

Pulse width low

Write

t

WEH (Minimum)

we

3.0

ns

Pulse width high

Write

t

AWS (Minimum)

wr addr setup -> we

2.0

ns

Write

tAWH (Minimum)

wr addr hold -> we

0.0

ns

Write

tDS (Minimum)

din setup -> we

2.0

ns

Write

tDH (Minimum)

din hold -> we

0.0

ns

Write/Read

t

DD (Maximum)

din -> dout

4.6

ns

rd addr = wr addr

Read

t

AD (Maximum)

rd addr -> dout

3.1

ns

Read

t

OZX (Maximum)

oe -> dout

1.6

ns

Read

tOXZ (Maximum)

oe -> dout

2.0

ns

Sync RAM

Write

tCYC (Minimum)

cycle time

8.0

ns

Write

t

CLKL (Minimum)

clk

3.0

ns

Pulse width low

Write

t

CLKH (Minimum)

clk

3.0

ns

Pulse width high

Write

t

WCS (Minimum)

we setup -> clk

2.0

ns

Write

tWCH (Minimum)

we hold -> clk

0.0

ns

Write

tACS (Minimum)

wr addr setup -> clk

2.0

ns

Write

tACH (Minimum)

wr addr hold -> clk

0.0

ns

Write

tDCS (Minimum)

wr data setup -> clk

2.0

ns

Write

t

DCH (Minimum)

wr data hold -> clk

0.0

ns

Write/Read

t

CD (Maximum)

clk -> dout

3.5

ns

rd addr = wr addr

Read

tAD (Maximum)

rd addr -> dout

3.1

ns

Read

tOZX (Maximum)

oe -> dout

1.6

ns

Read

tOXZ (Maximum)

oe -> dout

2.0

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AT40K40LV-3BQC | FPGA, 2304 CLBS, 40000 GATES, PQFP144 |

| AT40K40LV-3DQC | FPGA, 2304 CLBS, 40000 GATES, PQFP208 |

| AT40K40LV-3EQC | FPGA, 2304 CLBS, 40000 GATES, PQFP240 |

| AT40K40LV-3FQC | FPGA, 2304 CLBS, 40000 GATES, PQFP304 |

| AT40KEL040KW1SB | FPGA, 2304 CLBS, 50000 GATES, PQFP160 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT40K40LV-3BGI | 功能描述:IC FPGA 3.3V 2304 CELL 352BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:AT40K/KLV 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應商設備封裝:120-CPGA(34.55x34.55) |

| AT40K40LV-3BQC | 功能描述:IC FPGA 3.3V 2304 CELL 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:AT40K/KLV 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應商設備封裝:120-CPGA(34.55x34.55) |

| AT40K40LV-3BQI | 功能描述:IC FPGA 3.3V 2304 CELL 144TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:AT40K/KLV 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應商設備封裝:120-CPGA(34.55x34.55) |

| AT40K40LV-3CGC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| AT40K40LV-3CQC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購,3分鐘左右您將得到回復。