- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4375 > APA600-FG676I (Microsemi SoC)IC FPGA PROASIC+ 600K 676-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | APA600-FG676I |

| 廠商: | Microsemi SoC |

| 文件頁(yè)數(shù): | 140/178頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA PROASIC+ 600K 676-FBGA |

| 標(biāo)準(zhǔn)包裝: | 40 |

| 系列: | ProASICPLUS |

| RAM 位總計(jì): | 129024 |

| 輸入/輸出數(shù): | 454 |

| 門(mén)數(shù): | 600000 |

| 電源電壓: | 2.3 V ~ 2.7 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 676-BGA |

| 供應(yīng)商設(shè)備封裝: | 676-FBGA(27x27) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)當(dāng)前第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)

ProASICPLUS Flash Family FPGAs

2- 54

v5.9

Embedded Memory Specifications

This section discusses ProASICPLUS SRAM/FIFO embedded

memory and its interface signals, including timing

diagrams that show the relationships of signals as they

pertain to single embedded memory blocks (Table 2-51).

Table 2-13 on page 2-21 shows basic SRAM and FIFO

configurations. Simultaneous read and write to the same

location must be done with care. On such accesses the DI

bus is output to the DO bus. Refer to the ProASICPLUS

RAM and FIFO Blocks application note for more

information.

Enclosed Timing Diagrams—SRAM Mode:

Embedded Memory Specifications

The difference between synchronous transparent and

pipeline modes is the timing of all the output signals

from the memory. In transparent mode, the outputs will

change within the same clock cycle to reflect the data

requested by the currently valid access to the memory. If

clock cycles are short (high clock speed), the data

requires most of the clock cycle to change to valid values

(stable signals). Processing of this data in the same clock

cycle is nearly impossible. Most designers add registers at

all outputs of the memory to push the data processing

into the next clock cycle. An entire clock cycle can then

be used to process the data. To simplify use of this

memory

setup,

suitable

registers

have

been

implemented as part of the memory primitive and are

available to the user in the synchronous pipeline mode.

In this mode, the output signals will change shortly after

the second rising edge, following the initiation of the

read access.

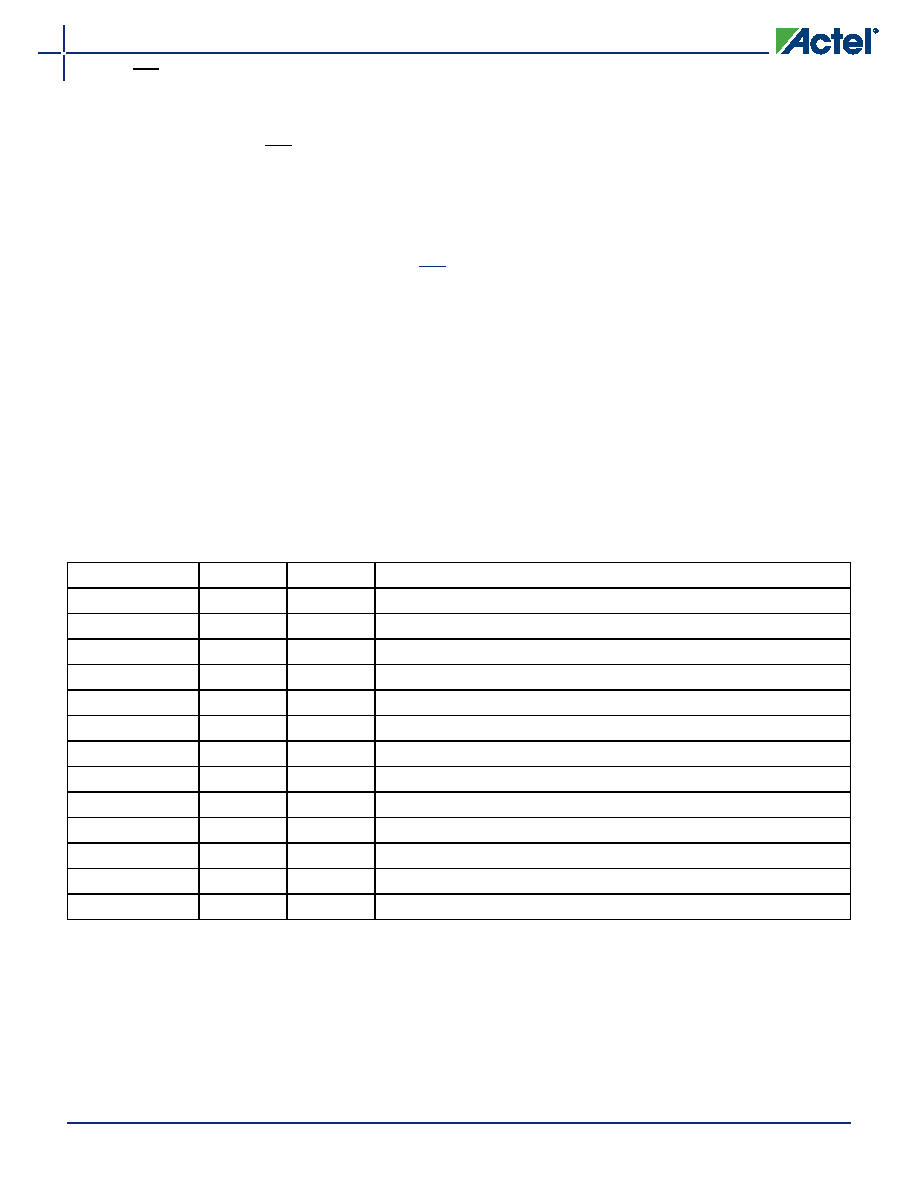

Table 2-51 Memory Block SRAM Interface Signals

SRAM Signal

Bits

In/Out

Description

WCLKS

1

In

Write clock used on synchronization on write side

RCLKS

1

In

Read clock used on synchronization on read side

RADDR[0:7]

8

In

Read address

RBLKB

1

In

True read block select (active Low)

RDB

1

In

True read pulse (active Low)

WADDR[0:7]

8

In

Write address

WBLKB

1

In

Write block select (active Low)

DI[0:8]

9

In

Input data bits [0:8], [8] can be used for parity In

WRB

1

In

Negative true write pulse

DO[0:8]

9

Out

Output data bits [0:8], [8] can be used for parity Out

RPE

1

Out

Read parity error (active High)

WPE

1

Out

Write parity error (active High)

PARODD

1

In

Selects odd parity generation/detect when high, even when low

Note: Not all signals shown are used in all modes.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ABB90DHRD | CONN CARD EXTEND 180POS .050" |

| ACB85DHLT | CONN EDGECARD 170PS .050 DIP SLD |

| EP2AGX65CU17C6N | IC ARRIA II GX FPGA 65K 358UBGA |

| IDT70V24L15PFG | IC SRAM 64KBIT 15NS 100TQFP |

| IDT71T75602S166PFG | IC SRAM 18MBIT 166MHZ 100TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| APA600-FG896A | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:Automotive-Grade ProASIC Flash Family FPGAs |

| APA600-FGB | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA600-FGES | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:ProASIC Flash Family FPGAs |

| APA600-FGG256 | 功能描述:IC FPGA PROASIC+ 600K 256-FBGA RoHS:是 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:ProASICPLUS 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| APA600-FGG256A | 功能描述:IC FPGA PROASIC+ 600K 256-FBGA RoHS:是 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:ProASICPLUS 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。