- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366544 > AM53CF94JC (ADVANCED MICRO DEVICES INC) Enhanced SCSI-2 Controller (ESC) PDF資料下載

參數(shù)資料

| 型號: | AM53CF94JC |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 總線控制器 |

| 英文描述: | Enhanced SCSI-2 Controller (ESC) |

| 中文描述: | SCSI BUS CONTROLLER, PQCC84 |

| 封裝: | PLASTIC, LCC-84 |

| 文件頁數(shù): | 28/76頁 |

| 文件大小: | 735K |

| 代理商: | AM53CF94JC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

P R E L I M I N A R Y

AMD

28

Am53CF94/Am53CF96

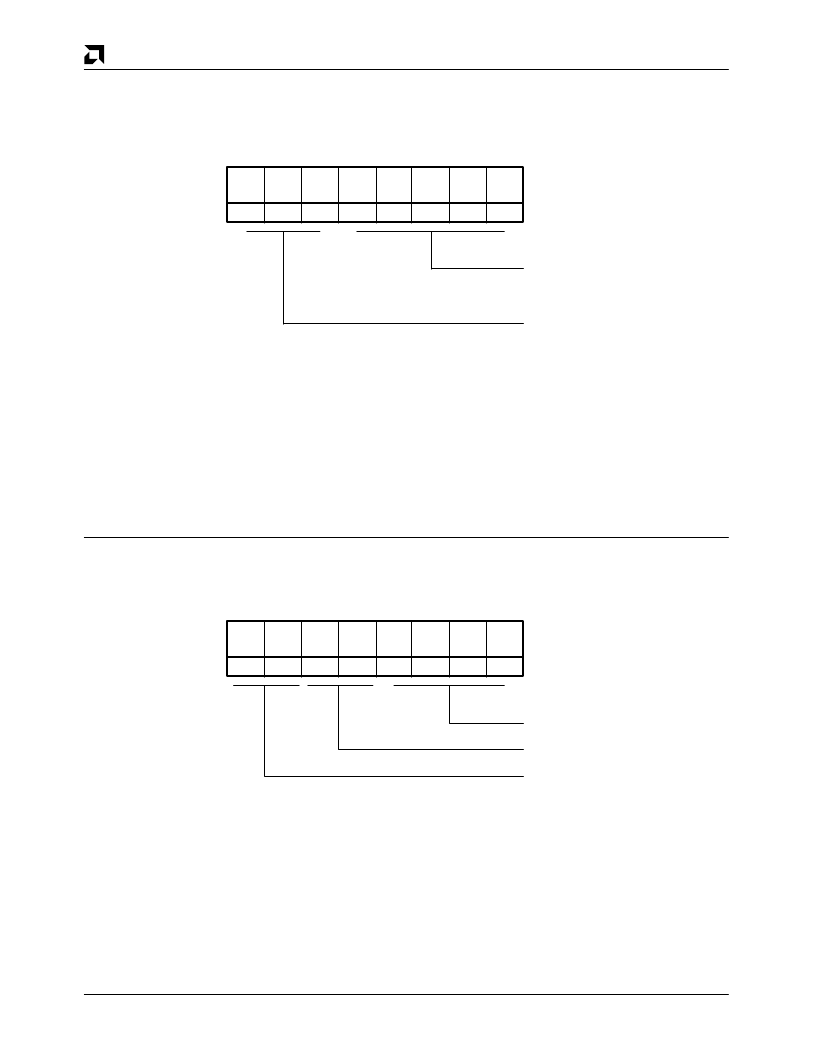

Current FIFO/Internal State Register (07H) Read

Current FIFO/Internal State Register

CFISREG

Address: 07

H

Type: Read

7

6

5

4

3

2

1

0

IS2

IS1

IS0

CF4

CF3

CF2

CF1

CF0

0

0

0

0

0

0

0

0

Internal State 2:0

Current FIFO 4:0

17348B-26

This register has two fields, the Current FIFO field and

the Internal State field.

CFISREG – Bits 7:5 – IS 2:0 – Internal State 2:0

The Internal State Register (ISREG) tracks the progress

of a sequence-type command.

The IS 2:0 bits are duplicated from the IS 2:0 field in the

Internal State Register (ISREG) in the normal mode. If

the device is in the test mode, (see CNTLREG1, bit 3)

IS 0 is set to indicate that the offset value is non-zero.

A non-zero value indicates that synchronous data

transfer can continue. A zero value indicates that the

synchronous offset count has been reached and no

more data can be transferred until an acknowledge is

received.

CFISREG – Bits 4:0 – CF 4:0 – Current FIFO 4:0

The CF 4:0 bits are the binary coded value of the num-

ber of bytes in the FIFO. These bits should not be read

when the device is transferring data since this count

may not be stable.

Synchronous Offset Register (07H) Write

Synchronous Offset Register

SOFREG

Address: 07

H

Type: Write

7

6

5

4

3

2

1

0

SO3

SO2

SO1

SO0

RAD1

RAD0

RAA1

RAA0

0

0

0

0

0

0

0

0

REQ

/

ACK

Assertion 1:0

Synchronous Offset 3:0

REQ

/

ACK

Deassertion 1:0

17348B-27

The Synchronous Offset Register (SOFREG) controls

REQ

/

ACK

deassertion/assertion delay and stores a

4-bit count of the number of bytes that can be sent to

(or received from) the SCSI bus during synchronous

transfers without an

ACK

(or

REQ

). Bytes exceeding

the threshold will be sent one byte at a time

(asynchronously). That is, each byte will require an

ACK

/

REQ

handshake. To set up an asynchronous

transfer, the SOFREG is set to zero. The SOFREG is set

to zero after a hard or soft reset.

SOFREG – Bits 7:6 – RAD 1:0

These bits may be programmed to control the deasser-

tion delay of the

REQ

and

ACK

signals during synchro-

nous transfers. Deassertion delay is expressed as input

clock cycles, and depends on the implementation of

FASTCLK. (See CNTLREG3, bit 3)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Am53CF94JCW | Enhanced SCSI-2 Controller (ESC) |

| Am53CF94KC | Enhanced SCSI-2 Controller (ESC) |

| Am53CF94KCW | Enhanced SCSI-2 Controller (ESC) |

| Am53CF96 | Enhanced SCSI-2 Controller (ESC) |

| Am53CF96JC | Enhanced SCSI-2 Controller (ESC) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM53CF94JCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Enhanced SCSI-2 Controller (ESC) |

| AM53CF94KC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Enhanced SCSI-2 Controller (ESC) |

| AM53CF94KCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Enhanced SCSI-2 Controller (ESC) |

| AM53CF96 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Enhanced SCSI-2 Controller (ESC) |

| AM53CF96JC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Enhanced SCSI-2 Controller (ESC) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。