- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366540 > AM42DL1622DT70IT (ADVANCED MICRO DEVICES INC) Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 2 Mbit (128 K x 16-Bit) Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | AM42DL1622DT70IT |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 存儲(chǔ)器 |

| 英文描述: | Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 2 Mbit (128 K x 16-Bit) Static RAM |

| 中文描述: | SPECIALTY MEMORY CIRCUIT, PBGA69 |

| 封裝: | 8 X 11 MM, FBGA-69 |

| 文件頁(yè)數(shù): | 28/128頁(yè) |

| 文件大?。?/td> | 650K |

| 代理商: | AM42DL1622DT70IT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)

26

Am42DL16x2D

February 6, 2004

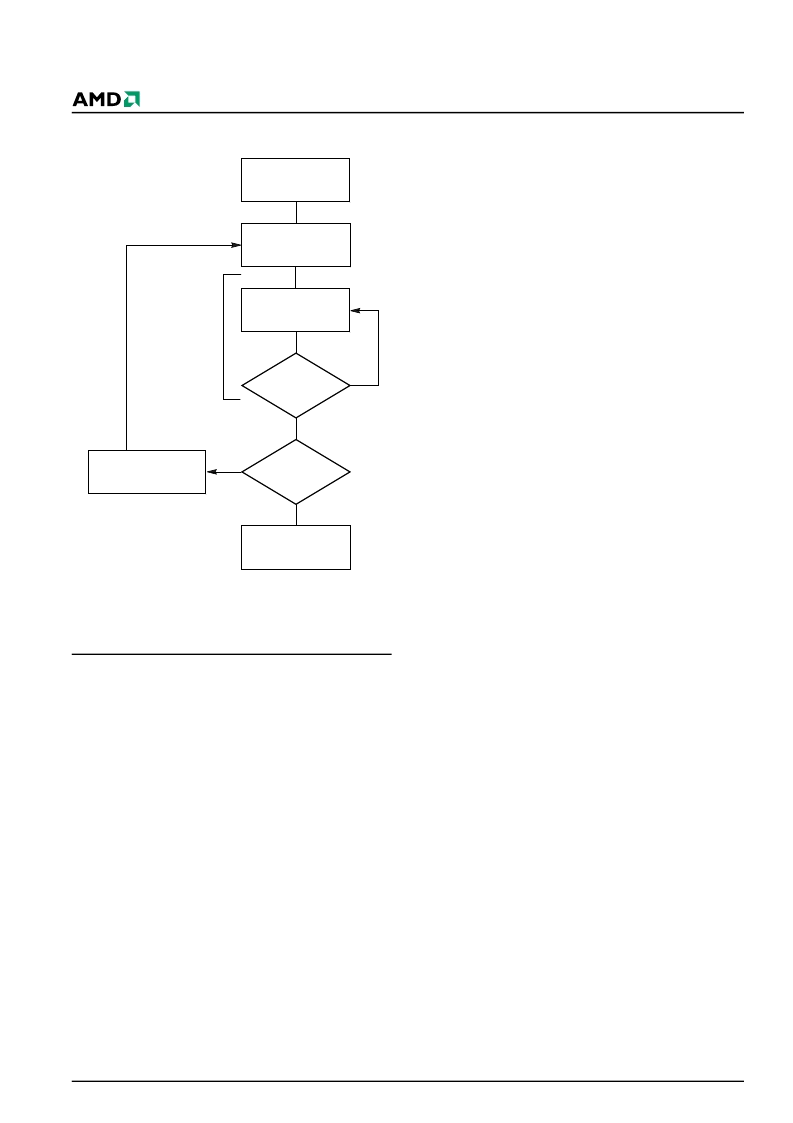

Figure 3.

Program Operation

Chip Erase Command Sequence

Chip erase is a six bus cycle operation. The chip erase

command sequence is initiated by writing two unlock

cycles, followed by a set-up command. Two additional

unlock write cycles are then followed by the chip erase

command, which in turn invokes the Embedded Erase

algorithm. The device does not require the system to

preprogram prior to erase. The Embedded Erase algo-

rithm automatically preprograms and verifies the entire

memory for an all zero data pattern prior to electrical

erase. The system is not required to provide any con-

trols or timings during these operations. Table 14

shows the address and data requirements for the chip

erase command sequence.

When the Embedded Erase algorithm is complete,

that bank returns to reading array data and addresses

are no longer latched. The system can determine the

status of the erase operation by using DQ7, DQ6,

DQ2, or RY/BY#. Refer to the Write Operation Status

section for information on these status bits.

Any commands written during the chip erase operation

are ignored. However, note that a

hardware reset

im-

mediately terminates the erase operation. If that

occurs, the chip erase command sequence should be

reinitiated once that bank has returned to reading

array data, to ensure data integrity.

Figure 4 illustrates the algorithm for the erase opera-

tion. Refer to the Flash Erase and Program Operations

tables in the AC Characteristics section for parame-

ters, and Figure 20 section for timing diagrams.

Sector Erase Command Sequence

Sector erase is a six bus cycle operation. The sector

erase command sequence is initiated by writing two

unlock cycles, followed by a set-up command. Two ad-

ditional unlock cycles are written, and are then

followed by the address of the sector to be erased, and

the sector erase command. Table 14 shows the ad-

dress and data requirements for the sector erase

command sequence.

The device does not require the system to preprogram

prior to erase. The Embedded Erase algorithm auto-

matically programs and verifies the entire memory for

an all zero data pattern prior to electrical erase. The

system is not required to provide any controls or tim-

ings during these operations.

After the command sequence is written, a sector erase

time-out of 50 μs occurs. During the time-out period,

additional sector addresses and sector erase com-

mands may be written. Loading the sector erase buffer

may be done in any sequence, and the number of sec-

tors may be from one sector to all sectors. The time

between these additional cycles must be less than

50 μs, otherwise erasure may begin. Any sector erase

address and command following the exceeded

time-out may or may not be accepted. It is recom-

mended that processor interrupts be disabled during

this time to ensure all commands are accepted. The

interrupts can be re-enabled after the last Sector

Erase command is written.

Any command other than

Sector Erase or Erase Suspend during the

time-out period resets that bank to reading array

data.

The system must rewrite the command se-

quence and any additional addresses and commands.

The system can monitor DQ3 to determine if the sec-

tor erase timer has timed out (See the section on DQ3:

Sector Erase Timer.). The time-out begins from the ris-

ing edge of the final WE# pulse in the command

sequence.

When the Embedded Erase algorithm is complete, the

bank returns to reading array data and addresses are

no longer latched. Note that while the Embedded

Erase operation is in progress, the system can read

data from the non-erasing bank. The system can de-

termine the status of the erase operation by reading

DQ7, DQ6, DQ2, or RY/BY# in the erasing bank. Refer

START

Write Program

Command Sequence

Data Poll

from System

Verify Data

No

Yes

Last Address

No

Yes

Programming

Completed

Increment Address

Embedded

Program

algorithm

in progress

Note:

See Table 14 for program command sequence.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM42DL1622DT85IS | Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 2 Mbit (128 K x 16-Bit) Static RAM |

| AM42DL1622DT85IT | Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 2 Mbit (128 K x 16-Bit) Static RAM |

| AM42DL1632DB30IS | Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 2 Mbit (128 K x 16-Bit) Static RAM |

| AM42DL1632DB30IT | Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 2 Mbit (128 K x 16-Bit) Static RAM |

| AM42DL1632DT85IS | Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 2 Mbit (128 K x 16-Bit) Static RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM42DL1622DT85I | 制造商:Spansion 功能描述:COMBO 1MX16/2MX8 FLASH + 128KX16 SRAM 3V/3.3V 69FBGA - Trays |

| AM42DL1622DT85IS | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 2 Mbit (128 K x 16-Bit) Static RAM |

| AM42DL1622DT85IT | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 2 Mbit (128 K x 16-Bit) Static RAM |

| AM42DL1624DB30IT | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 4 Mbit (256 K x 16-Bit) Static RAM |

| AM42DL1624DB35IT | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Am29DL16xD 16 Megabit (2 M x 8-Bit/1 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 4 Mbit (256 K x 16-Bit) Static RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。