- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362262 > AM29LV160BT-90SC x8/x16 Flash EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | AM29LV160BT-90SC |

| 英文描述: | x8/x16 Flash EEPROM |

| 中文描述: | x8/x16閃存EEPROM |

| 文件頁(yè)數(shù): | 8/35頁(yè) |

| 文件大?。?/td> | 744K |

| 代理商: | AM29LV160BT-90SC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)

8

Am29LV040B

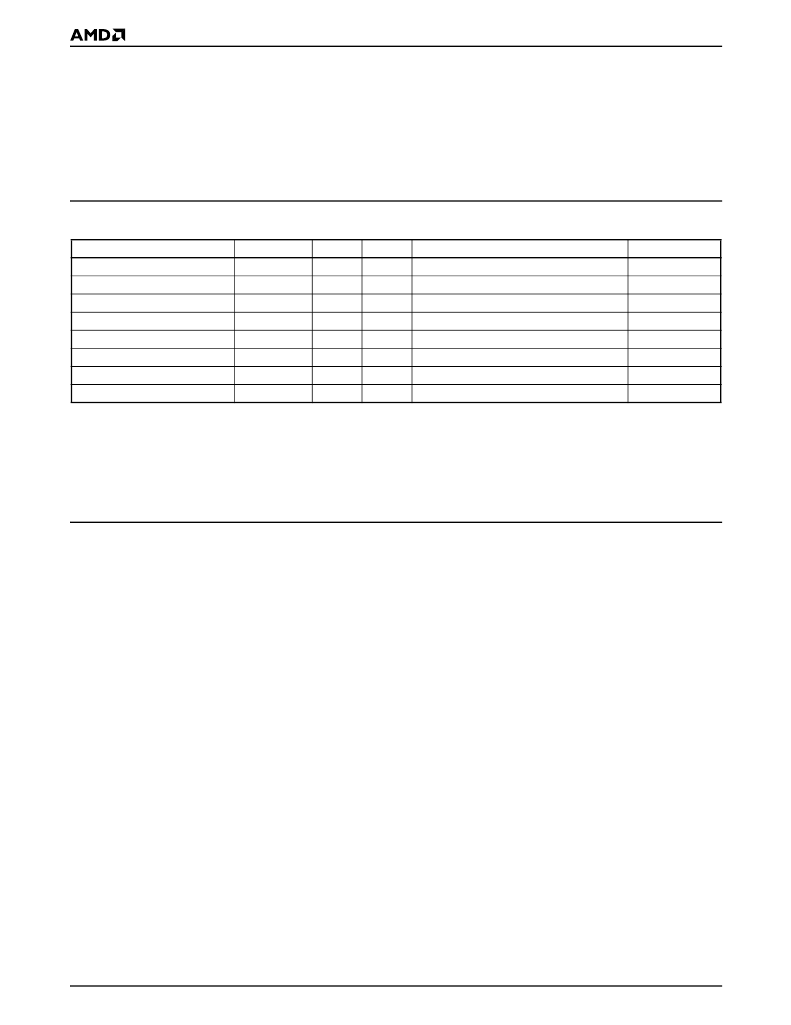

DEVICE BUS OPERATIONS

This section describes the requirements and use of the

device bus operations, which are initiated through the

internal command register. The command register

itself does not occupy any addressable memory loca-

tion. The register is composed of latches that store the

commands, along with the address and data informa-

tion needed to execute the command. The contents of

the register serve as inputs to the internal state

machine. The state machine outputs dictate the func-

tion of the device. Table 1 lists the device bus

operations, the inputs and control levels they require,

and the resulting output. The following subsections

describe each of these operations in further detail.

Table 1.

Am29LV040B Device Bus Operations

Legend:

L = Logic Low = V

IL

, H = Logic High = V

IH

, V

ID

= 12.0

±

0.5 V, X = Don’t Care, A

IN

= Address In, D

IN

= Data In, D

OUT

= Data Out

Notes:

1. Addresses are A18–A0.

2. The sector protect and sector unprotect functions may also be implemented via programming equipment. See the “Sector

Protection/Unprotection” section.

Requirements for Reading Array Data

To read array data from the outputs, the system must

drive the CE# and OE# pins to V

IL

. CE# is the power

control and selects the device. OE# is the output

control and gates array data to the output pins. WE#

should remain at V

IH

.

The internal state machine is set for reading array data

upon device power-up, or after a hardware reset. This

ensures that no spurious alteration of the memory

content occurs during the power transition. No

command is necessary in this mode to obtain array

data. Standard microprocessor read cycles that assert

valid addresses on the device address inputs produce

valid data on the device data outputs. The device

remains enabled for read access until the command

register contents are altered.

See “Reading Array Data” for more information. Refer

to the AC Read Operations table for timing specifica-

tions and to Figure 11 for the timing diagram. I

CC1

in the

DC Characteristics table represents the active current

specification for reading array data.

Writing Commands/Command Sequences

To write a command or command sequence (which

includes programming data to the device and erasing

sectors of memory), the system must drive WE# and

CE# to V

IL

, and OE# to V

IH

.

The device features an

Unlock Bypass

mode to facili-

tate faster programming. Once the device enters the

Unlock Bypass mode, only two write cycles are

required to program a byte, instead of four. The “Byte

Program Command Sequence” section has details on

programming data to the device using both standard

and Unlock Bypass command sequences.

An erase operation can erase one sector, multiple sec-

tors, or the entire device. Table 2 indicates the address

space that each sector occupies. A “sector address”

consists of the address bits required to uniquely select

a sector. The “Command Definitions” section has

details on erasing a sector or the entire chip, or sus-

pending/resuming the erase operation.

After the system writes the autoselect command

sequence, the device enters the autoselect mode. The

system can then read autoselect codes from the

internal register (which is separate from the memory

array) on DQ7–DQ0. Standard read cycle timings apply

Operation

CE#

L

L

OE#

L

H

X

H

X

H

H

X

WE#

H

L

X

H

X

L

L

X

Addresses (Note 1)

A

IN

A

IN

X

X

X

Sector Address, A6 = L, A1 = H, A0 = L

Sector Address, A6 = H, A1 = H, A0 = L

A

IN

DQ0–DQ7

D

OUT

D

IN

High-Z

High-Z

High-Z

D

IN

, D

OUT

D

IN

, D

OUT

D

IN

Read

Write

Standby

Output Disable

Reset

Sector Protect (Note 2)

Sector Unprotect (Note 2)

Temporary Sector Unprotect

V

CC

±

0.3 V

L

X

L

L

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM29LV160BT-90SE | x8/x16 Flash EEPROM |

| AM29LV160BT-90SI | x8/x16 Flash EEPROM |

| AM29LV200BB120WAE | EEPROM|FLASH|128KX16/256KX8|CMOS|BGA|48PIN|PLASTIC |

| AM29LV200BB120WAI | EEPROM|FLASH|128KX16/256KX8|CMOS|BGA|48PIN|PLASTIC |

| AM29LV200BB-55REC | EEPROM|FLASH|128KX16/256KX8|CMOS|TSSOP|48PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM29LV160DB120EI | 制造商:Advanced Micro Devices 功能描述: |

| AM29LV160DB-120EIT | 制造商:Spansion 功能描述:FLASH PARALLEL 3V/3.3V 16MBIT 2MX8/1MX16 120NS 48TSOP - Tape and Reel |

| AM29LV160DB120WCCT | 制造商:Advanced Micro Devices 功能描述: |

| am29lv160db120wcis | 制造商:Advanced Micro Devices 功能描述: |

| AM29LV160DB70EC | 制造商:FLASH29LV160 功能描述:AM29LV160DB-70EC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。