- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366350 > AM27C040-90JE (Advanced Micro Devices, Inc.) 4 Megabit (512 K x 8-Bit) CMOS EPROM PDF資料下載

參數(shù)資料

| 型號: | AM27C040-90JE |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | 4 Megabit (512 K x 8-Bit) CMOS EPROM |

| 中文描述: | 4兆位(512畝× 8位)的CMOS存儲器 |

| 文件頁數(shù): | 1/13頁 |

| 文件大?。?/td> | 175K |

| 代理商: | AM27C040-90JE |

FINAL

Publication#

14971

Issue Date:

May 1998

Rev:

G

Amendment/

0

Am27C040

4 Megabit (512 K x 8-Bit) CMOS EPROM

DISTINCTIVE CHARACTERISTICS

I

Fast access time

— Available in speed options as fast as 90 ns

I

Low power consumption

— <10 μA typical CMOS standby current

I

JEDEC-approved pinout

— Plug-in upgrade for 1 Mbit and 2 Mbit EPROMs

— Easy upgrade from 28-pin JEDEC EPROMs

I

Single +5 V power supply

I

±

10% power supply tolerance standard

I

100% Flashrite programming

— Typical programming time of 1 minute

I

Latch-up protected to 100 mA from –1 V to

V

CC

+ 1 V

I

High noise immunity

I

Compact 32-pin DIP, PDIP, PLCC packages

GENERAL DESCRIPTION

The Am27C040 is a 4 Mbit ultraviolet erasable pro-

grammable read-only memory. It is organized as 512K

bytes, operates from a single +5 V supply, has a static

standby mode, and features fast single address loca-

tion programming. The device is available in windowed

ceramic DIP packages and plastic one-time program-

mable (OTP) packages.

Data can be typically accessed in less than 90 ns, al-

lowing high-performance microprocessors to operate

without any WAIT states. The device offers separate

Output Enable (OE#) and Chip Enable (CE#) controls,

thus eliminating bus contention in a multiple bus micro-

processor system.

AMD’s CMOS process technology provides high

speed, low power, and high noise immunity. Typical

power consumption is only 100 mW in active mode,

and 50 μW in standby mode.

All signals are TTL levels, including programming sig-

nals. Bit locations may be programmed singly, in

blocks, or at random. The device supports AMD’s

Flashrite programming algorithm (100 μs pulses) re-

sulting in typical programming time of 1 minute.

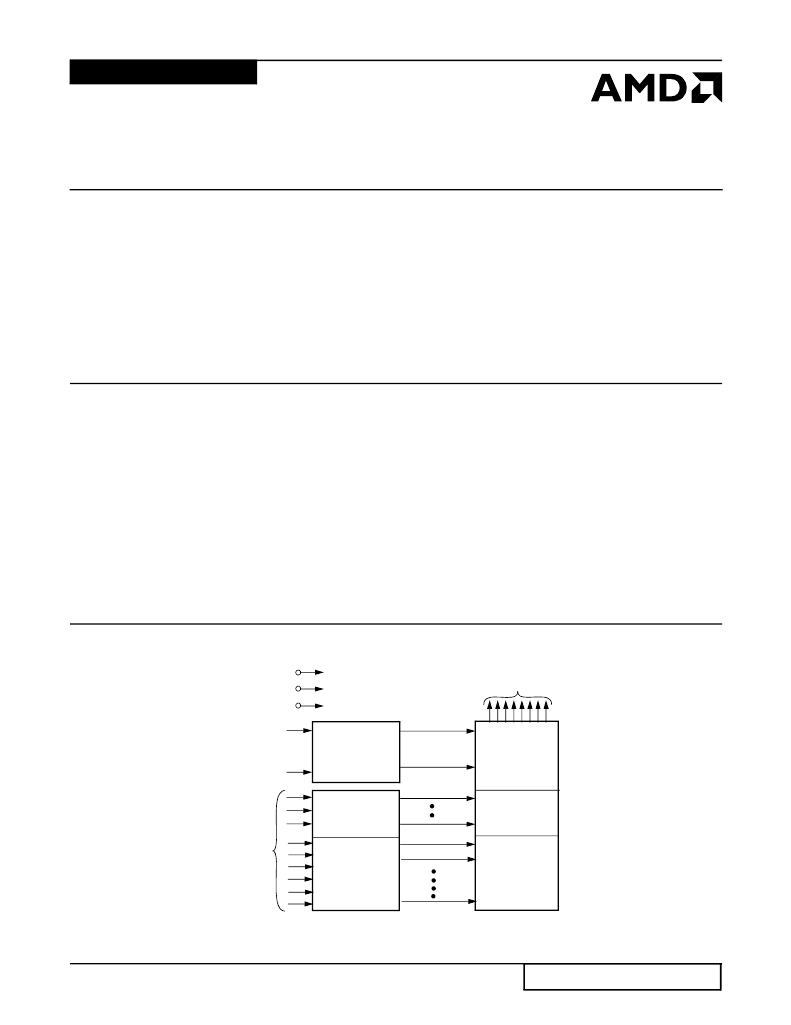

BLOCK DIAGRAM

14971G-1

A0–A18

Address

Inputs

CE#/PGM#

OE#

V

CC

V

SS

V

PP

Data Outputs

DQ0–DQ7

Output

Buffers

Y

Gating

4,194,304-Bit

Cell Matrix

X

Decoder

Y

Decoder

Output Enable

Chip Enable

and

Prog Logic

相關PDF資料 |

PDF描述 |

|---|---|

| AM27C040-90JI | 4 Megabit (512 K x 8-Bit) CMOS EPROM |

| AM27C040-90PC | 4 Megabit (512 K x 8-Bit) CMOS EPROM |

| AM27C040-90PE | SEAL,NEOPRENE,CYLINDRICAL CONNECTR& |

| AM27C040-120DEB | 4 Megabit (512 K x 8-Bit) CMOS EPROM |

| AM27C040-120DIB | 4 Megabit (512 K x 8-Bit) CMOS EPROM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AM27C040-90JI | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:4 Megabit (512 K x 8-Bit) CMOS EPROM |

| AM27C040-90LC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 EPROM |

| AM27C040-90LCB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 EPROM |

| AM27C040-90PC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:4 Megabit (512 K x 8-Bit) CMOS EPROM |

| AM27C040-90PE | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:4 Megabit (512 K x 8-Bit) CMOS EPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。