- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4105 > AM1808BZWT4 (Texas Instruments)IC ARM9 MPU 361NFBGA PDF資料下載

參數(shù)資料

| 型號: | AM1808BZWT4 |

| 廠商: | Texas Instruments |

| 文件頁數(shù): | 54/264頁 |

| 文件大小: | 0K |

| 描述: | IC ARM9 MPU 361NFBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | ARM9 |

| 處理器類型: | ARM 微處理器 |

| 速度: | 456MHz |

| 電壓: | 1.25 V ~ 1.35 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 361-LFBGA |

| 供應(yīng)商設(shè)備封裝: | 361-NFBGA(16x16) |

| 包裝: | 托盤 |

| 其它名稱: | 296-28241 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁當(dāng)前第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁第251頁第252頁第253頁第254頁第255頁第256頁第257頁第258頁第259頁第260頁第261頁第262頁第263頁第264頁

SPRS653E – FEBRUARY 2010 – REVISED MARCH 2014

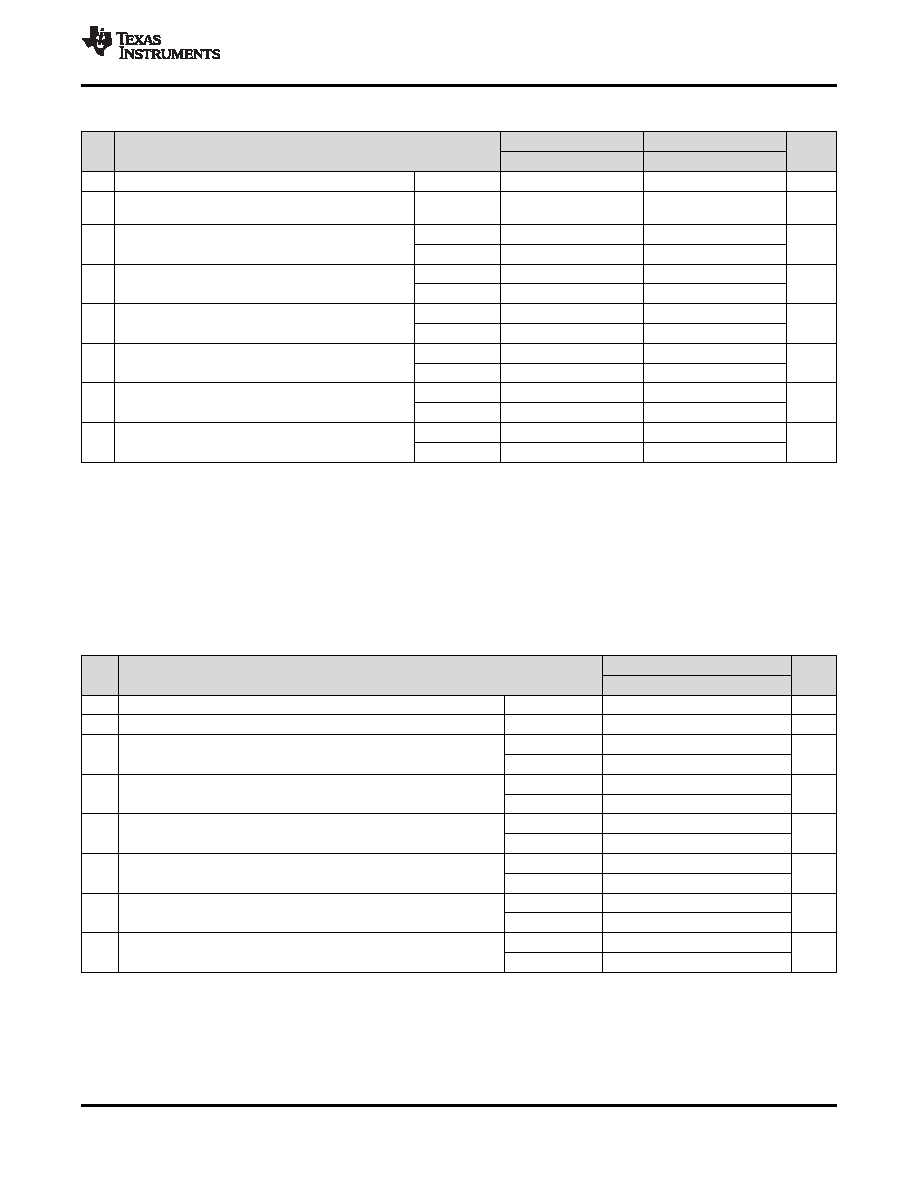

1.3V, 1.2V

1.1V

NO.

UNIT

MIN

MAX

MIN

MAX

2

tc(CKRX)

Cycle time, CLKR/X

CLKR/X ext

2P or 20(2)(3)

2P or 25(2) (4)

ns

Pulse duration, CLKR/X high or

3

tw(CKRX)

CLKR/X ext

P - 1(5)

P - 1(6)

ns

CLKR/X low

CLKR int

15

18

Setup time, external FSR high before

5

tsu(FRH-CKRL)

ns

CLKR low

CLKR ext

5

CLKR int

6

Hold time, external FSR high after

6

th(CKRL-FRH)

ns

CLKR low

CLKR ext

3

CLKR int

15

18

7

tsu(DRV-CKRL)

Setup time, DR valid before CLKR low

ns

CLKR ext

5

CLKR int

3

8

th(CKRL-DRV)

Hold time, DR valid after CLKR low

ns

CLKR ext

3

CLKX int

15

18

Setup time, external FSX high before

10

tsu(FXH-CKXL)

ns

CLKX low

CLKX ext

5

CLKX int

6

Hold time, external FSX high after

11

th(CKXL-FXH)

ns

CLKX low

CLKX ext

3

(1)

CLKRP = CLKXP = FSRP = FSXP = 0. If polarity of any of the signals is inverted, then the timing references of that signal are also

inverted.

(2)

P = ASYNC3 period in ns. For example, when the ASYNC clock domain is running at 100 MHz, use 10 ns.

(3)

Use whichever value is greater. Minimum CLKR/X cycle times must be met, even when CLKR/X is generated by an internal clock

source. The minimum CLKR/X cycle times are based on internal logic speed; the maximum usable speed may be lower due to EDMA

limitations and AC timing requirements.

(4)

Use whichever value is greater. Minimum CLKR/X cycle times must be met, even when CLKR/X is generated by an internal clock

source. The minimum CLKR/X cycle times are based on internal logic speed; the maximum usable speed may be lower due to EDMA

limitations and AC timing requirements.

(5)

This parameter applies to the maximum McBSP frequency. Operate serial clocks (CLKR/X) in the reasonable range of 40/60 duty cycle.

(6)

This parameter applies to the maximum McBSP frequency. Operate serial clocks (CLKR/X) in the reasonable range of 40/60 duty cycle.

1.0V

NO.

UNIT

MIN

MAX

2

tc(CKRX)

Cycle time, CLKR/X

CLKR/X ext

2P or 26.6(2)(3)

ns

3

tw(CKRX)

Pulse duration, CLKR/X high or CLKR/X low

CLKR/X ext

P - 1(4)

ns

CLKR int

21

5

tsu(FRH-CKRL)

Setup time, external FSR high before CLKR low

ns

CLKR ext

10

CLKR int

6

th(CKRL-FRH)

Hold time, external FSR high after CLKR low

ns

CLKR ext

3

CLKR int

21

7

tsu(DRV-CKRL)

Setup time, DR valid before CLKR low

ns

CLKR ext

10

CLKR int

3

8

th(CKRL-DRV)

Hold time, DR valid after CLKR low

ns

CLKR ext

3

CLKX int

21

10

tsu(FXH-CKXL)

Setup time, external FSX high before CLKX low

ns

CLKX ext

10

CLKX int

6

11

th(CKXL-FXH)

Hold time, external FSX high after CLKX low

ns

CLKX ext

3

(1)

CLKRP = CLKXP = FSRP = FSXP = 0. If polarity of any of the signals is inverted, then the timing references of that signal are also

inverted.

(2)

P = ASYNC3 period in ns. For example, when the ASYNC clock domain is running at 100 MHz, use 10 ns.

(3)

Use whichever value is greater. Minimum CLKR/X cycle times must be met, even when CLKR/X is generated by an internal clock

source. The minimum CLKR/X cycle times are based on internal logic speed; the maximum usable speed may be lower due to EDMA

limitations and AC timing requirements.

(4)

This parameter applies to the maximum McBSP frequency. Operate serial clocks (CLKR/X) in the reasonable range of 40/60 duty cycle.

Copyright 2010–2014, Texas Instruments Incorporated

Peripheral Information and Electrical Specifications

147

Product Folder Links: AM1808

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT7133SA25PF8 | IC SRAM 32KBIT 25NS 100TQFP |

| 1-84984-3 | CONN FFC 13POS 1.00MM VERT PCB |

| MPC8541EVTALF | IC MPU POWERQUICC III 783-FCPBGA |

| IDT7134LA20JG8 | IC SRAM 32KBIT 20NS 52PLCC |

| 4-1734839-8 | CONN FPC 48POS .5MM RT ANG SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM1808BZWTA3 | 功能描述:微處理器 - MPU ARM MicroProc RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| AM1808BZWTA4 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:AM1808 ARM Microprocessor |

| AM1808BZWTD3 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:AM1808 ARM Microprocessor |

| AM1808BZWTD4 | 功能描述:微處理器 - MPU ARM MicroProc RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| AM1808BZWTT3 | 制造商:Texas Instruments 功能描述:IC ARM9 CORTEX MPU 361NFBGA 制造商:Texas Instruments 功能描述:AM1808BZWTT3 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。