- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362173 > AHF2812DF-MSTR Analog IC PDF資料下載

參數(shù)資料

| 型號(hào): | AHF2812DF-MSTR |

| 英文描述: | Analog IC |

| 中文描述: | 模擬IC |

| 文件頁數(shù): | 3/9頁 |

| 文件大小: | 103K |

| 代理商: | AHF2812DF-MSTR |

3

AHE2812D

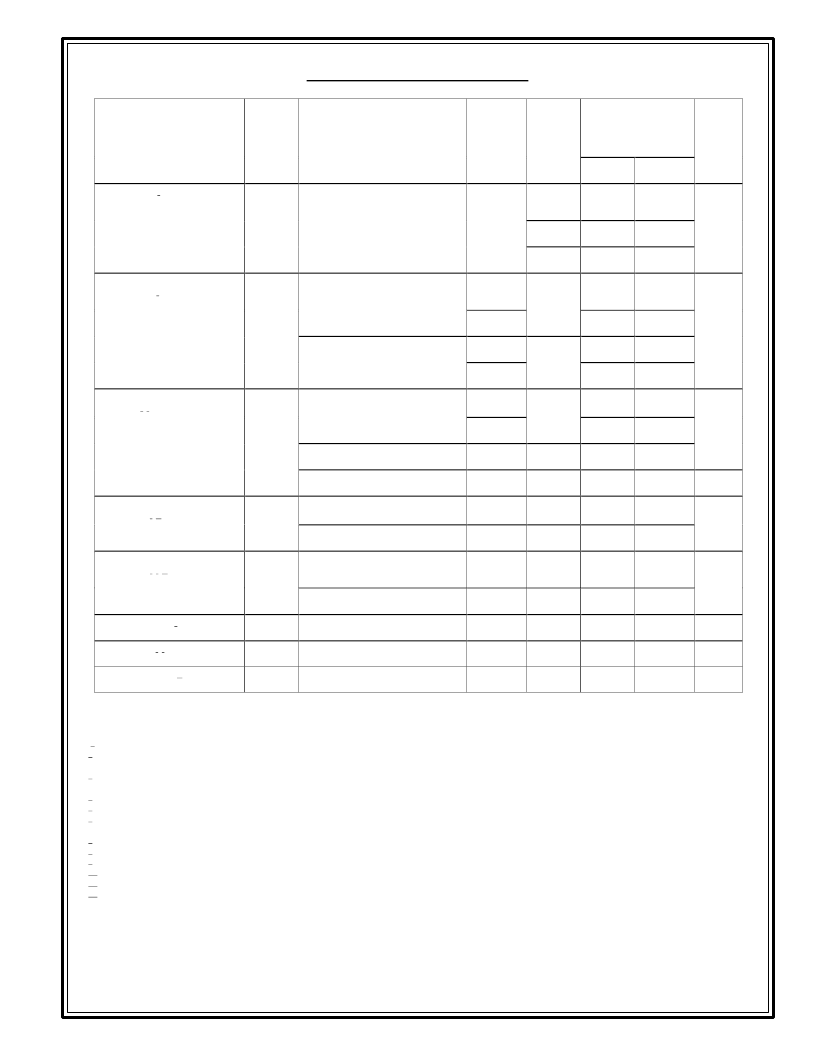

TABLE I. Electrical Performance Characteristics - Continued

Test

Symbol

Conditions

-55

°

C

≤

T

C

≤

+125

°

C

V

IN

= 28 V dc ±5%, C

L

= 0 unless

otherwise specified

Group A

Subgroups

Device

Type

Limits

Unit

Min

Max

Switching

9/

frequency

F

S

I

OUT

= ±625 mA

4,5,6

01

225

275

KHz

02

225

245

03

250

275

Output response to step transient

load changes

VO

TLOAD

50 percent load to/from 100 percent load

4

All

-300

+300

mV pk

5,6

-450

+450

No load to/from 50 percent load

4

All

-500

+500

5,6

-750

+750

Recovery time step transient load

changes

TT

LOAD

50 percent load to/from 100 percent load

4

All

70

μs

5,6

100

No load to 50 percent load

4,5,6

All

1500

50 percent load to no load

4,5,6

All

5

ms

Output response to transient step

line changes

VO

TLINE

Input step 17 TO 40 V dc

4,5,6

All

1200

mV pk

Input step 40 TO 17 V dc

4,5,6

All

-1500

Recovery time transient step

line changes

TT

LINE

Input step 17 TO 40 V dc

4,5,6

All

4

ms

Input step 40 TO 17 V dc

4,5,6

All

4

Turn on overshoot

9/

VTon

OS

I

OUT

= 0 and ±625 mA

4,5,6

All

600

mV pk

Turn on delay

2/ 9/

Ton

D

I

OUT

= 0 and ±625 mA

4,5,6

All

10

ms

Load fault recovery

12/

Tr

LF

4,5,6

All

10

ms

Notes:

1/ Recovery time is measured from the initiation of the transient to where V

OUT

has returned to within ±1 percent of V

OUT

at 50 percent load.

2/ Turn on delay time measurement is for either a step application of power at the input or the removal of a ground signal from the inhibit pin (pin 2) while power is applied to the

input.

3/ An overload is that condition with a load in excess of the rated load but less than that necessary to trigger the short circuit protection and is the condition of maximum

power dissipation.

4/ Total power at both outputs. For operation at 16 V dc input, derate output power by 33 percent.

5/ Input step transition time between 2 and 10 microseconds.

6/ Capacitive load may be any value from 0 to the maximum limit without compromising dc performance. A capacitive load in excess of the maximum limit will not

disturb loop stability but may interfere with the operation of the load fault detection circuitry, appearing as a short circuit during turn on.

7/ Load step transition time between 2 and 10 microseconds.

8/ Bandwidth guaranteed by design. Tested for 20 KHz to 2 MHz.

9/ Tested at each output.

10/ When operating with unbalanced loads, at least 25 percent of the load must be on the positive output to maintain regulation.

11/ Parameter guaranteed by line and load regulation tests.

12/ Parameter shall be tested as part of design characterization and after design or process changes. Thereafter parameters shall be guaranteed to the limits specified in Table I.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AHF2812DF-SLV | Analog IC |

| AHF2812D-MSTR | Analog IC |

| AHF2812D-SLV | Analog IC |

| AHF28XX | 28V Input, Single and Dual Output |

| AHL7 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AHF2812DF-SLV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| AHF2812D-MSTR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| AHF2812D-SLV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| AHF2812S | 制造商:International Rectifier 功能描述:DC/DC CONVERTER, MINIMUM SCREENING - Bulk |

| AHF2812S/CH | 制造商:International Rectifier 功能描述:DC/DC CONVERTER, CLASS H - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。