- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374044 > ADV601 (Analog Devices, Inc.) Low Cost Multiformat Video Codec PDF資料下載

參數(shù)資料

| 型號(hào): | ADV601 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 視頻Codec |

| 英文描述: | Low Cost Multiformat Video Codec |

| 中文描述: | 低成本多格式視頻解碼器 |

| 文件頁(yè)數(shù): | 18/52頁(yè) |

| 文件大?。?/td> | 606K |

| 代理商: | ADV601 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

ADV601

–18–

REV. 0

DSP Interface Pins

(

Continued

)

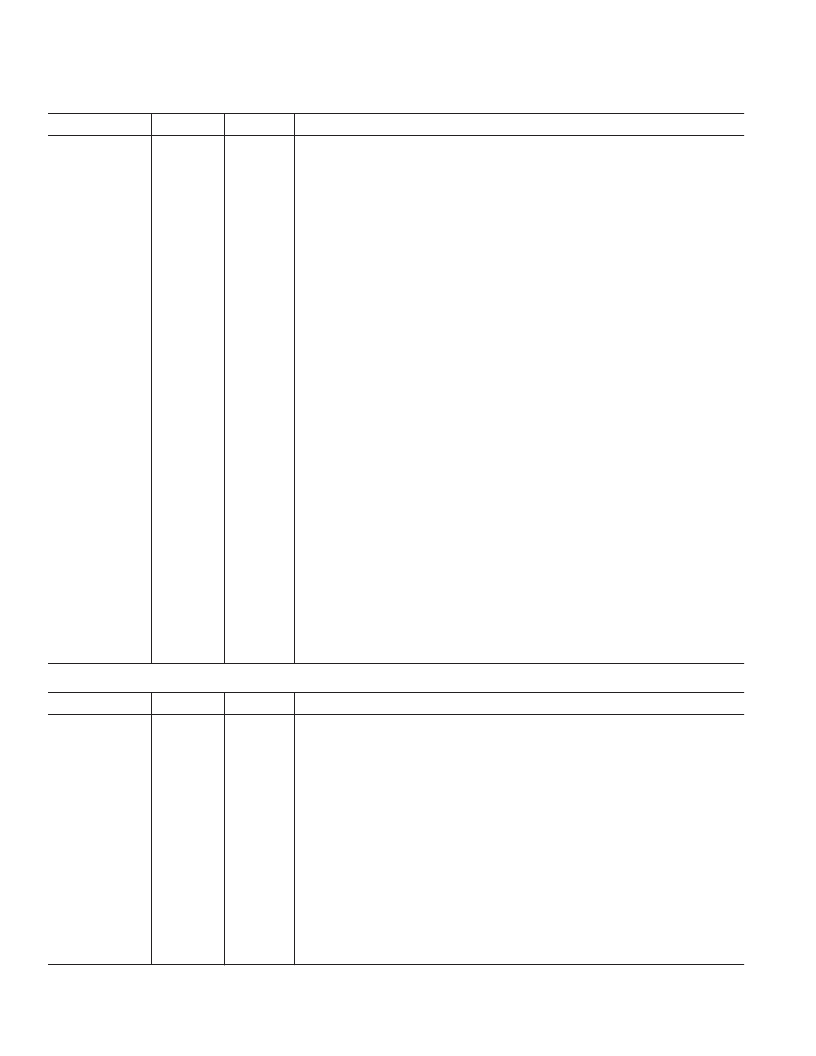

Name

Pins

I/O

Description

TF

1

O

Serial Transmit Frame Sync. Connect this pin to an optional, external DSP’s serial

interface RF Sync pin. If no DSP is present, leave this pin unconnected. This pin is

compatible with 30 pF loads.

The TF pin is the transmit frame synch. When transmitting, the ADV601 marks

new frames with a HI pulse driven out on TF one serial clock period before the

frame begins. Whether transmitting or receiving, the synch signals may transition

back from HI to LO at any time, provided the HI and LO times of TF or RF are at

least one TCLK period in duration. Note that the DSP must be set for external

framing on receive data. Frame size for ADV601 serial data transmission is 52 slots

of 16 bits.

Note that the Mode Control register must be set to indicate whether or not the

external DSP is present.

Receive Frame Sync. Connect this pin to an optional, external DSP’s serial inter-

face TF Sync pin. If no DSP is present, tie this pin to ground. This pin is compat-

ible with 30 pF loads.

The RF pin is the receive frame synch. When receiving, the ADV601 requires that

the DSP marks new frames with a LO to HI transition driven in on RF one serial

clock period before the frame begins. Whether transmitting or receiving, the synch

signals may transition back from HI to LO at any time provided the HI and LO

times of TF or RF are at least one TCLK period in duration. Note that the DSP

must be set for internal framing on transmit data. When receiving, the frame size

for ADV601 serial data is 84 slots of 16 bits.

Note that the Mode Control register must be set to indicate whether or not the

external DSP is present.

DSP Interrupt. Connect this pin to an optional, external DSP’s hardware interrupt

pin (IRQ2). If no DSP is present, this pin may be left unconnected. This pin is

compatible with 30 pF loads.

The

DIRQ

pin on the ADV601 provides an optional method for signalling the DSP

that a new packet of field statistics is being transmitted and can be used system-

wide for signalling that a new video field has begun. Because the ADV601 asserts

DIRQ

throughout statistics transmission and bin width reception, the DSP’s inter-

rupts should be set for edge-sensitivity.

Note that the Mode Control register must be set to indicate whether or not the

external DSP is present.

RF

1

I

DIRQ

1

O

Host Interface Pins

Name

Pins

I/O

Description

DATA[31:0]

32

I/O

Host Data Bus. These pins make up a 32-bit wide host data bus. The host controls

this asynchronous bus with the

WR

,

RD

, BE, and

CS

pins to communicate with

the ADV601. These pins are compatible with 30 pF loads.

Host DWord Address Bus. These two address pins let you address the ADV601’s

four directly addressable host interface registers. For an illustration of how this

addressing works, see the Control and Write Register Map figure and Status and

Read Register Map figure. The ADR bits permit register addressing as follows:

ADR1

ADR0

DWord

Address Byte Address

0

0

0

0x00

0

1

1

0x04

1

0

2

0x08

1

1

3

0x0C

Host Byte Enable pins. These four input pins allow selection of which bytes in

ADV601 direct and indirect registers will be accessed through the Host Interface;

BE0

—least significant byte

BE3

—most significant byte. For a 32-bit interface only,

tie these pins to ground, making all bytes available.

ADR[1:0]

2

I

BE0

–

BE3

4

I

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV601JS | Low Cost Multiformat Video Codec |

| ADV601LC | Ultralow Cost Video Codec |

| ADV601LCJST | Ultralow Cost Video Codec |

| ADV7120KP30 | CMOS 80 MHz, Triple 8-Bit Video DAC |

| ADV7120 | CMOS 80 MHz, Triple 8-Bit Video DAC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV601E-VIDEOPIPE | 制造商:Analog Devices 功能描述:VIDEOPIPE |

| ADV601JS | 制造商:Analog Devices 功能描述:Multiformat Video Codec 160-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADV601JS12 | 制造商:Analog Devices 功能描述:Multiformat Video Codec 160-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:DIGITAL VIDEO CODEC REV 1.2 - Bulk |

| ADV601LC | 制造商:AD 制造商全稱:Analog Devices 功能描述:Ultralow Cost Video Codec |

| ADV601LCERAG1266B-0.5 | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。