- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374034 > ADSP-2163BP-66 (ANALOG DEVICES INC) DSP Microcomputers with ROM PDF資料下載

參數(shù)資料

| 型號: | ADSP-2163BP-66 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | DSP Microcomputers with ROM |

| 中文描述: | 24-BIT, 16.67 MHz, OTHER DSP, PQCC68 |

| 封裝: | PLASTIC, LCC-68 |

| 文件頁數(shù): | 3/39頁 |

| 文件大小: | 243K |

| 代理商: | ADSP-2163BP-66 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

REV. 0

ADSP-216x

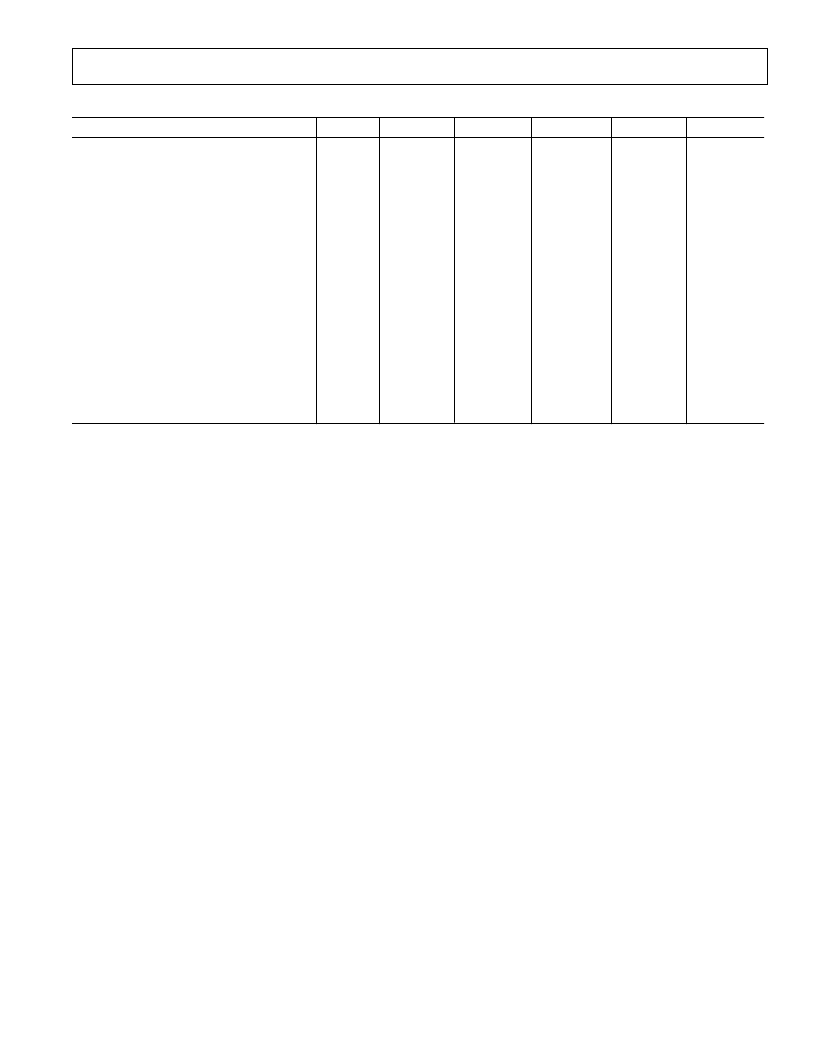

Table I. ADSP-216x ROM-Programmed Processor Features

Feature

2161

2162

2163

2164

2165

2166

Data Memory (RAM)

Program Memory (ROM)

Program Memory (RAM)

Timer

Serial Port 0 (Multichannel)

Serial Port 1

Supply Voltage

Speed Grades

(Instruction Cycle Time)

10.24 MHz

(97.6 ns)

13.00 MHz (

76.9 ns

)

16.67 MHz

(60 ns)

20.00 MHz (

50 ns

)

25 MHz

(40 ns)

Packages

68-Lead PLCC

80-Lead MQFP

Temperature Grades

K

Commercial,

0

°

C to +70

°

C

B

Industrial,

–40

°

C to +85

°

C

1/2K

8K

1/2K

8K

1/2K

4K

1/2K

4K

4K

12K

1K

5 V

4K

12K

1K

3.3 V

5 V

3.3 V

5 V

3.3 V

Development Tools

The ADSP-216x processors are supported by a complete set of

tools for system development. The ADSP-2100 Family Devel-

opment Software includes C and assembly language tools that

allow programmers to write code for any of the ADSP-216x

processors. The ANSI C compiler generates ADSP-216x assem-

bly source code, while the runtime C library provides ANSI-

standard and custom DSP library routines. The ADSP-216x

assembler produces object code modules that the linker com-

bines into an executable file. The processor simulators provide

an interactive instruction-level simulation with a reconfigurable,

windowed user interface. A PROM splitter utility generates

PROM programmer compatible files.

EZ-ICE

in-circuit emulators allow debugging of ADSP-21xx

systems by providing a full range of emulation functions such

as modification of memory and register values and execution

breakpoints. EZ-LAB

demonstration boards are complete DSP

systems that execute EPROM-based programs.

The EZ-Kit Lite is a very low-cost evaluation/development

platform that contains both the hardware and software needed

to evaluate the ADSP-21xx architecture.

Additional details and ordering information are available in the

ADSP-2100 Family Software & Hardware Development Tools

data

sheet (ADDS-21xx-TOOLS). This data sheet can be requested

from any Analog Devices sales office or distributor.

Additional Information

This data sheet provides a general overview of ADSP-216x

processor functionality. For detailed design information on the

architecture and instruction set, refer to the

ADSP-2100 Family

User’s Manual

, Third Edition, available from Analog Devices.

ARCHITECTURE OVERVIEW

Figure 1 shows a block diagram of the ADSP-216x architecture.

The processors contain three independent computational units:

the ALU, the multiplier/accumulator (MAC), and the shifter.

The computational units process 16-bit data directly and have

provisions to support multiprecision computations. The ALU

performs a standard set of arithmetic and logic operations;

division primitives are also supported. The MAC performs

single-cycle multiply, multiply/add, and multiply/subtract opera-

tions. The shifter performs logical and arithmetic shifts, normal-

ization, denormalization, and derive exponent operations. The

shifter can be used to efficiently implement numeric format control

including multiword floating-point representations.

The internal result (R) bus directly connects the computational

units so that the output of any unit may be used as the input of

any unit on the next cycle.

A powerful program sequencer and two dedicated data address

generators ensure efficient use of these computational units.

The sequencer supports conditional jumps, subroutine calls,

and returns in a single cycle. With internal loop counters and

loop stacks, the ADSP-216x executes looped code with zero

overhead—no explicit jump instructions are required to main-

tain the loop.

Two data address generators (DAGs) provide addresses for

simultaneous dual operand fetches (from data memory and

program memory). Each DAG maintains and updates four

address pointers. Whenever the pointer is used to access data

(indirect addressing), it is post-modified by the value of one of

four modify registers. A length value may be associated with

each pointer to implement automatic modulo addressing for

circular buffers. The circular buffering feature is also used by

the serial ports for automatic data transfers to (and from) on-

chip memory.

EZ-ICE and EZ-LAB are registered trademarks of Analog Devices, Inc.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-2163BS-100 | 100V 1A ULTRA FAST LOW-LOSS CONTROLLED AVALANCHE RECTIFIER, SMA US1 SERIES, DO- |

| ADSP-2163BS-66 | DSP Microcomputers with ROM |

| ADSP-2163KS-100 | DSP Microcomputers with ROM |

| ADSP-2163KS-66 | DSP Microcomputers with ROM |

| ADSP-2164BS-40 | SWITCH SLIDE DP3T RT ANG L=6MM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2163BP-662 | 制造商:AD 制造商全稱:Analog Devices 功能描述:ADSP-2100 Family DSP Microcomputers |

| ADSP-2163BS-100 | 制造商:AD 制造商全稱:Analog Devices 功能描述:ADSP-2100 Family DSP Microcomputers |

| ADSP-2163BS-1002 | 制造商:AD 制造商全稱:Analog Devices 功能描述:ADSP-2100 Family DSP Microcomputers |

| ADSP-2163BS-66 | 制造商:AD 制造商全稱:Analog Devices 功能描述:ADSP-2100 Family DSP Microcomputers |

| ADSP-2163BS-662 | 制造商:AD 制造商全稱:Analog Devices 功能描述:ADSP-2100 Family DSP Microcomputers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。