- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374016 > ADMCF340-EVALKIT (Analog Devices, Inc.) Circular Connector; No. of Contacts:7; Series:MS27497; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:10; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:10-99 RoHS Compliant: No PDF資料下載

參數(shù)資料

| 型號: | ADMCF340-EVALKIT |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 圓形連接器 |

| 英文描述: | Circular Connector; No. of Contacts:7; Series:MS27497; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:10; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:10-99 RoHS Compliant: No |

| 中文描述: | DashDSPTM 64無鉛閃存混合信號增強的DSP與模擬前端 |

| 文件頁數(shù): | 16/40頁 |

| 文件大小: | 415K |

| 代理商: | ADMCF340-EVALKIT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

REV. 0

ADMCF340

–16–

In general, the on-times of the PWM signals in double update

mode are defined by:

T

AH

= (

PWMCHA

1

+

PWMCHA

2

–

PWMDT

1

–

PWMDT

2

)

×

T

CK

T

AL

= (

PWMTM

1

+

PWMTM

2

–

PWMCHA

1

–

PWMCHA

2

–

PWMDT

1

–

PWMDT

2

)

×

T

CK

d

T

T

PWMCHA

PWMTM

PWMCHA

PWMTM

PWMDT

PWMTM

PWMDT

PWMTM

d

T

T

PWMTM

PWMTM

PWMCHA

PWMTM

PWMTM

PWMCHA

PWMDT

+

1

PWMDT

PWMTM

PWMTM

AH

AH

S

AL

AL

S

=

=

+

+

+

+

=

=

+

+

(

)

+

+

+

(

)

1

2

1

2

1

2

1

2

1

2

1

1

2

2

1

2

2

–

because of the completely general case in double update mode,

the switching period is given by:

T

PWNMTM

PWMTM

T

S

CK

=

+

(

)

×

1

2

Again, the values of

T

AH

and

T

AL

are constrained to lie between

zero and

T

S

.

PWM signals similar to those illustrated in Figure 7 and Figure 8 can

be produced on the BH, BL, CH, and CL outputs by programming

the PWMCHB and PWMCHC Registers in a manner identical

to that described for PWMCHA.

The PWM controller does not produce any PWM outputs until

all of the PWMTM, PWMCHA, PWMCHB, and PWMCHC

Registers have been written to at least once. After these registers

have been written, the counters in the three-phase timing unit

are enabled. Writing to these registers also starts the main PWM

timer. If during initialization, the PWMTM Register is written

before the PWMCHA, PWMCHB, and PWMCHC Registers, the

first PWMSYNC pulse (and interrupt if enabled) will be generated

(1.5

×

T

CK

×

PWMTM) seconds after the initial write to the

PWMTM Register in single update mode. In double update mode,

the first PWMSYNC pulse will be generated (T

CK

×

PWMTM)

seconds after the initial write to the PWMTM Register in single

update mode.

Effective PWM Resolution

In single update mode, the same values of PWMCHA, PWMCHB,

and PWMCHC are used to define the on-times in both half

cycles of the PWM period. As a result, the effective resolution of

the PWM generation process is 2 T

CK

(or 100 ns for a 20 MHz

CLKOUT) since incrementing one of the duty cycle registers by

one changes the resultant on-time of the associated PWM signals

by T

CK

in each half period (or 2 T

CK

for the full period).

In double update mode, improved resolution is possible since

different values of the duty cycle registers are used to define the

on-times in both the first and second halves of the PWM period.

As a result, it is possible to adjust the on-time over the whole

period in increments of T

CK

. This corresponds to an effective

PWM resolution of T

CK

in double update mode (or 50 ns for a

20 MHz CLKOUT).

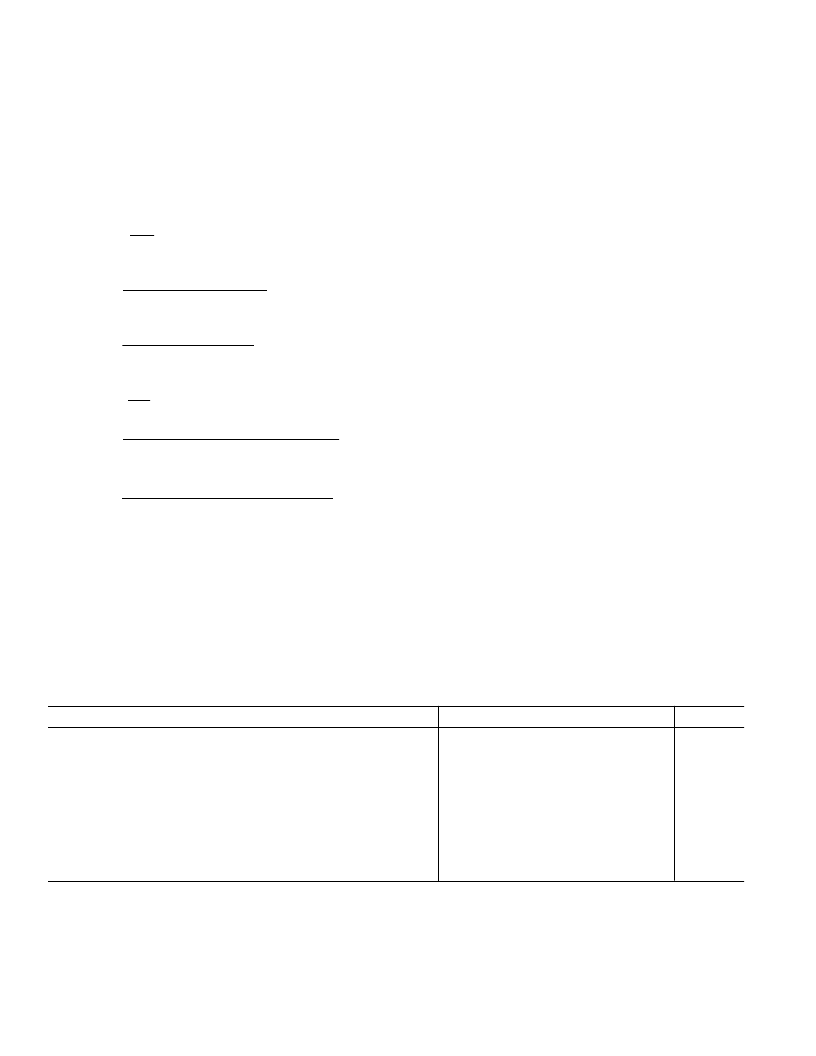

Table IV. Fundamental Characteristics of PWM Generation Unit of ADMCF340

16-BIT PWM TIMER

Parameter

Min

Typ

Max

Unit

Counter Resolution

Edge Resolution (Single Update Mode)

Edge Resolution (Double Update Mode)

Programmable Dead Time Range

Programmable Dead Time Increments

Programmable Pulse Deletion Range

Programmable Pulse Deletion Increments

PWM Frequency Range

PWMSYNC Pulsewidth (T

CRST

)

Gate Drive Chop Frequency Range

16

100

50

Bits

ns

ns

μ

s

ns

μ

s

ns

Hz

μ

s

MHz

0

102

100

0

50

51

153

0.05

0.02

12.8

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADMCF341 | DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF341BR | DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF341-EVALKIT | DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADN2811 | OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2811ACP-CML | OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADMCF340XSTB | 制造商:Analog Devices 功能描述: |

| ADMCF341 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

| ADMCF341BR | 制造商:Analog Devices 功能描述:DSP Fixed-Point/Floating-Point 16-Bit 20MHz 20MIPS 28-Pin SOIC W T/R |

| ADMCF341BRZ-REEL | 制造商:Analog Devices 功能描述: |

| ADMCF341-EVALKIT | 制造商:AD 制造商全稱:Analog Devices 功能描述:DashDSP⑩ 28-Lead Flash Mixed-Signal DSP with Enhanced Analog Front End |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。