- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378285 > ADCS7476AIMF (NATIONAL SEMICONDUCTOR CORP) 1MSPS, 12-/10-/8-Bit A/D Converters in 6-Lead SOT-23 PDF資料下載

參數(shù)資料

| 型號: | ADCS7476AIMF |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | ADC |

| 英文描述: | 1MSPS, 12-/10-/8-Bit A/D Converters in 6-Lead SOT-23 |

| 中文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO6 |

| 封裝: | SOT-23, 6 PIN |

| 文件頁數(shù): | 17/22頁 |

| 文件大小: | 514K |

| 代理商: | ADCS7476AIMF |

Applications Information

1.0 ADCS7476/77/78 OPERATION

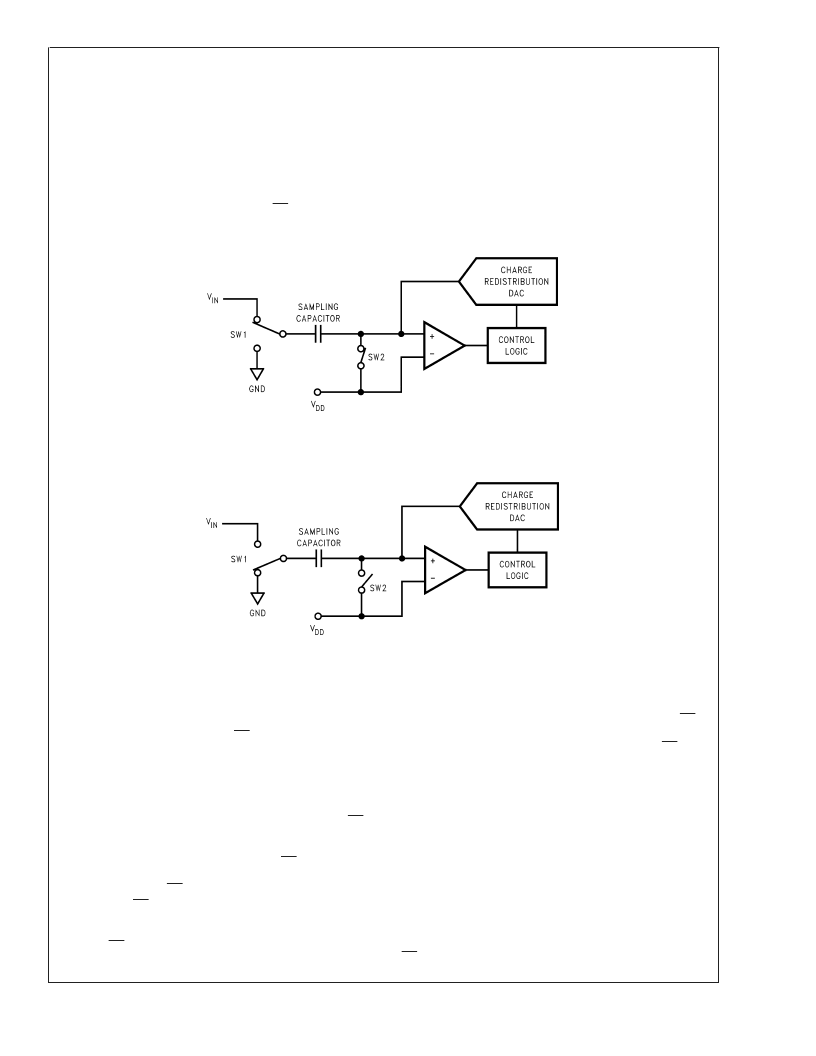

The

ADCS7476/77/78

analog-to-digital converters designed around a charge-

redistribution digital-to-analog converter. Simplified sche-

matics of the ADCS7476/77/78 in both track and hold opera-

tion are shown in Figures 4 and 5, respectively. In Figure 4,

the device is in track mode: switch SW1 connects the sam-

pling capacitor to the input, and SW2 balances the compara-

tor inputs. The device is in this state until CS is brought low,

at which point the device moves to hold mode.

are

successive-approximation

Figure 5 shows the device in hold mode: switch SW1 con-

nects the sampling capacitor to ground, maintaining the

sampled voltage, and switch SW2 unbalances the compara-

tor. The control logic then instructs the charge-redistribution

DAC to add or subtract fixed amounts of charge from the

sampling capacitor until the comparator is balanced. When

the comparator is balanced, the digital word supplied to the

DAC is the digital representation of the analog input voltage.

The device moves from hold mode to track mode on the 13th

rising edge of SCLK.

2.0 USING THE ADCS7476/77/78

Serial interface timing diagrams for theADCS7476/77/78 are

shown in Figures 1, 2, and 3. CS is chip select, which

initiates conversions on the ADCS7476/77/78 and frames

the serial data transfers. SCLK (serial clock) controls both

the conversion process and the timing of serial data. SDATA

is the serial data out pin, where a conversion result is found

as a serial data stream.

Basic operation of the ADCS7476/77/78 begins with CS

going low, which initiates a conversion process and data

transfer. Subsequent rising and falling edges of SCLK will be

labelled with reference to the falling edge of CS; for example,

"the third falling edge of SCLK" shall refer to the third falling

edge of SCLK after CS goes low.

At the fall of CS, the SDATA pin comes out of TRI-STATE,

and the converter moves from track mode to hold mode. The

input signal is sampled and held for conversion on the falling

edge of CS. The converter moves from hold mode to track

mode on the 13th rising edge of SCLK (see Figure 1, 2, or 3).

The SDATA pin will be placed back into TRI-STATE after the

16th falling edge of SCLK, or at the rising edge of CS,

whichever occurs first. After a conversion is completed, the

quiet time t

QUIET

must be satisfied before bringing CS low

again to begin another conversion.

Sixteen SCLK cycles are required to read a complete

sample from the ADCS7476/77/78. The sample bits (includ-

ing any leading or trailing zeroes) are clocked out on falling

edges of SCLK, and are intended to be clocked in by a

receiver on subsequent falling edges of SCLK. The

ADCS7476/77/78 will produce four leading zeroes on

SDATA, followed by twelve, ten, or eight data bits, most

significant first. After the data bits, the ADCS7477 will clock

out two trailing zeros, and the ADCS7478 will clock out four

trailing zeros. The ADCS7476 will not clock out any trailing

zeros; the least significant data bit will be valid on the 16th

falling edge of SCLK.

Depending upon the application, the first edge on SCLK after

CS goes low may be either a falling edge or a rising edge. If

20057709

FIGURE 4. ADCS7476/77/78 in Track Mode

20057710

FIGURE 5. ADCS7476/77/78 in Hold Mode

A

www.national.com

17

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADCS7476AIMFX | 1MSPS, 12-/10-/8-Bit A/D Converters in 6-Lead SOT-23 |

| ADCS7477 | 1MSPS, 12-/10-/8-Bit A/D Converters in 6-Lead SOT-23 |

| ADCS7477AIMF | 1MSPS, 12-/10-/8-Bit A/D Converters in 6-Lead SOT-23 |

| ADCS7477AIMFX | 1MSPS, 12-/10-/8-Bit A/D Converters in 6-Lead SOT-23 |

| ADCS7478 | 1MSPS, 12-/10-/8-Bit A/D Converters in 6-Lead SOT-23 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADCS7476AIMF | 制造商:Texas Instruments 功能描述:12BIT ADC 1MSPS SMD 7476 SOT236 |

| ADCS7476AIMF/NOPB | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 1MSPS,12-/10-/8B ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADCS7476AIMFE | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:1MSPS, 12-/10-/8-Bit A/D Converters in SOT-23 & LLP |

| ADCS7476AIMFE/NOPB | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADCS7476AIMFNOPB | 制造商:Texas Instruments 功能描述:Analog Digital Converter, Single, 12 Bit, 6 Pin, TSOP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。