- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6653 (Analog Devices, Inc.) IF Diversity Receiver PDF資料下載

參數(shù)資料

| 型號(hào): | AD6653 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | IF Diversity Receiver |

| 中文描述: | IF分集接收機(jī) |

| 文件頁數(shù): | 27/80頁 |

| 文件大小: | 1998K |

| 代理商: | AD6653 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

AD6653

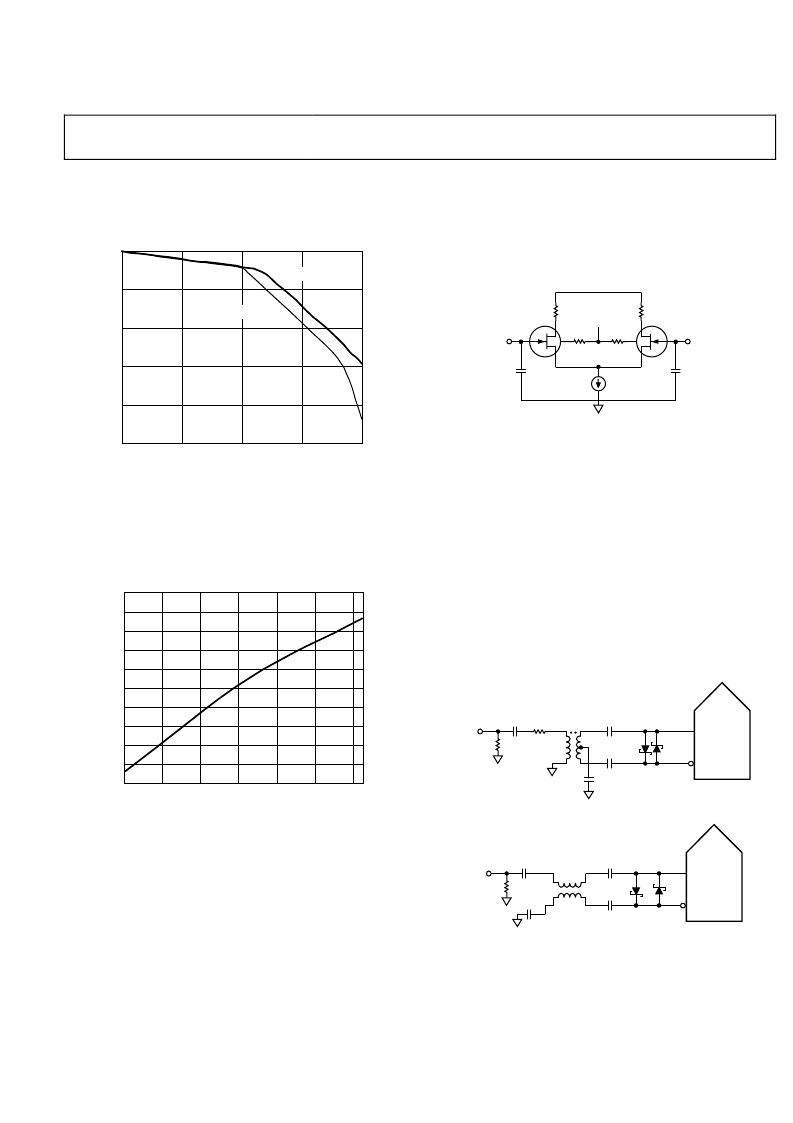

If the internal reference of the AD6653 is used to drive multiple

converters to improve gain matching, the loading of the reference

by the other converters must be considered. Figure 54 depicts

how the internal reference voltage is affected by loading.

Rev. 0 | Page 27 of 80

.0

0

–1.25

0

2

LOAD CURRENT (mA)

R

–0.25

–0.50

–0.75

–1.00

0.5

1.0

1.5

VREF = 0.5V

VREF = 1.0V

0

Figure 54. VREF Accuracy vs. Load

External Reference Operation

The use of an external reference may be necessary to enhance

the gain accuracy of the ADC or improve thermal drift charac-

teristics. Figure 55 shows the typical drift characteristics of the

internal reference in both 1.0 V and 0.5 V modes.

2.5

–2.5

–40

TEMPERATURE (°C)

R

2.0

1.5

1.0

0.5

0

–0.5

–1.0

–1.5

–2.0

–20

0

20

40

60

80

0

Figure 55. Typical VREF Drift

When the SENSE pin is tied to AVDD, the internal reference

is disabled, allowing the use of an external reference. An internal

reference buffer loads the external reference with an equivalent

6 kΩ load (see Figure 18). The internal buffer generates the

positive and negative full-scale references for the ADC core.

Therefore, the external reference must be limited to a maximum

of 1.0 V.

CLOCK INPUT CONSIDERATIONS

For optimum performance, the AD6653 sample clock inputs,

CLK+ and CLK, should be clocked with a differential signal.

The signal is typically ac-coupled into the CLK+ and CLK pins

via a transformer or capacitors. These pins are biased internally

(see Figure 56) and require no external bias.

1.2V

AVDD

2pF

2pF

CLK–

CLK+

0

Figure 56. Equivalent Clock Input Circuit

Clock Input Options

The AD6653 has a very flexible clock input structure. Clock input

can be a CMOS, LVDS, LVPECL, or sine wave signal. Regardless

of the type of signal being used, the clock source jitter is of the

most concern, as described in the Jitter Considerations section.

Figure 57 and Figure 58 show two preferred methods for clocking

the AD6653 (at clock rates up to 625 MHz). A low jitter clock

source is converted from a single-ended signal to a differential

signal, using an RF transformer. The back-to-back Schottky diodes

across the transformer secondary limit clock excursions into the

AD6653 to approximately 0.8 V p-p differential. This helps prevent

the large voltage swings of the clock from feeding through to other

portions of the AD6653 while preserving the fast rise and fall

times of the signal, which are critical to low jitter performance.

0.1μF

0.1μF

0.1μF

0.1μF

SCHOTTKY

DIODES:

HSMS2822

CLOCK

INPUT

50

100

CLK–

CLK+

ADC

AD6653

Mini-Circuits

ADT1–1WT, 1:1Z

XFMR

0

Figure 57. Transformer-Coupled Differential Clock (Up to 200 MHz)

0.1μF

0.1μF

1nF

CLOCK

INPUT

1nF

50

CLK–

CLK+

ADC

AD6653

SCHOTTKY

DIODES:

HSMS2822

0

Figure 58. Balun-Coupled Differential Clock (Up to 625 MHz)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6653-125EBZ | IF Diversity Receiver |

| AD6653BCPZ-125 | IF Diversity Receiver |

| AD6653BCPZ-150 | IF Diversity Receiver |

| AD6655BCPZ-1251 | IF Diversity Receiver |

| AD6655 | IF Diversity Receiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6653-125EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD6653 制造商:Analog Devices 功能描述:EVAL BD FOR AD6653 - Bulk 制造商:Analog Devices 功能描述:KIT EVALUATION BOARD AD6653 |

| AD6653-150EBZ | 制造商:Analog Devices 功能描述:EVAL BD FOR AD6653 - Bulk |

| AD6653BCPZ-125 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 |

| AD6653BCPZ-150 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 制造商:Analog Devices 功能描述:IC, RECEIVER, IF DIVERSITY, LFCSP64 |

| AD6654 | 制造商:Analog Devices 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。