- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373886 > AD6121ARS (ANALOG DEVICES INC) CDMA 3 V Receiver IF Subsystem with Integrated Voltage Regulator PDF資料下載

參數(shù)資料

| 型號(hào): | AD6121ARS |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | CDMA 3 V Receiver IF Subsystem with Integrated Voltage Regulator |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, DSO28 |

| 封裝: | SSOP-28 |

| 文件頁(yè)數(shù): | 2/16頁(yè) |

| 文件大小: | 258K |

| 代理商: | AD6121ARS |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

–2–

REV. B

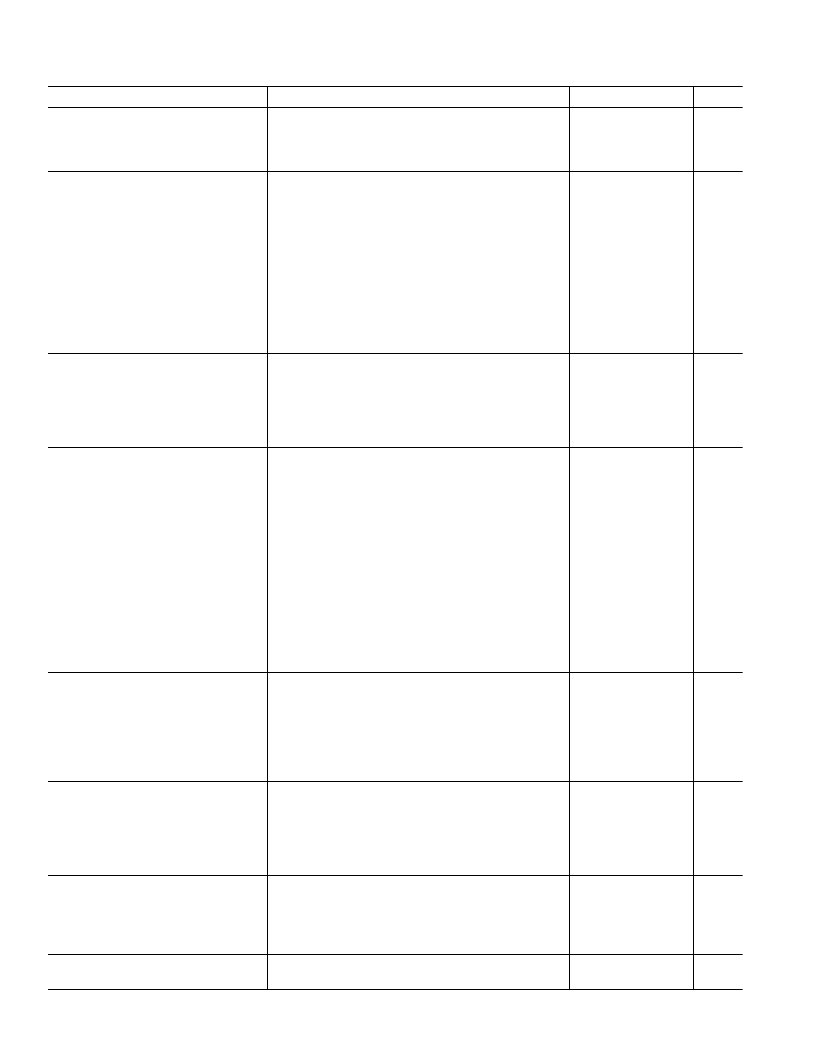

AD6121–SPECIFICATIONS

Specification

(T

A

= +25 C, V

CC

= 3.0 V, LO = 2 IF, REFIN = 1.23 V, LDO Enabled, unless otherwise

noted) Note: All power measurements in dBm are referred to 1 k unless Z

IN

is noted.

Conditions

Min

Typ

Max

Units

TOTAL GAIN

Maximum Gain

IF Amplifiers and Demodulator Powered Up

IF Amplifiers Powered Up and Demodulator Powered Down

IF Amplifier and Demodulator Powered Up

+47

+41.4

–47.5

dB

dB

dB

Minimum Gain

IF AMPLIFIER

CDMA and FM Input

Noise Figure

Input Third-Order Intercept

Input 1 dB Compression Point

Gain Flatness

CDMA Input Capacitance

CDMA Input Resistance

FM Input Capacitance

FM Input Resistance

Output Capacitance

Output Resistance

IF = 85.38 MHz

Maximum Gain

Maximum Gain

Maximum Gain

IF

±

630 kHz, CDMA Mode

Differential

Differential

Differential

Differential

Differential

Differential

5.9

–42.8

–51.6

±

0.25

2.8

850

2.3

670

1.35

1.1

dB

dBm

dBm

dB

pF

pF

pF

k

GAIN CONTROL INTERFACE

Gain Scaling

Gain Scaling Accuracy

Gain Control Response Time

Input Resistance at REFIN

Input Resistance at VGAIN

Using Internal Reference

Within a Gain Control Range of 90 dB

Minimum Gain to Maximum Gain

52.5

±

3

695

10

100

dB/V

dB/V

ns

M

k

DEMODULATOR

LO = 172.76 MHz , –15 dBm Referred to 50

,

Baseband Frequency = 1 MHz

Differential Input Impedance

Differential Input Capacitance at

Demodulator Input

Input Third Order Intercept

Demodulation Gain

I/Q Output

Differential Output Voltage

Bandwidth

Resistance

Quadrature Accuracy

Amplitude Balance

LO Input Impedance

LO Input Capacitance

1

k

2.9

–6.1

5.6

pF

dBm

dB

10 k

, 2 pF Differential Parallel Load Impedance

–3 dB

Single-Ended

700

16

630

mV p-p

MHz

Degree

dB

k

pF

±

2.5

±

0.35

±

0.1

1.5

4.16

Differential

Differential

CONTROL INTERFACES

Logic Threshold High

Logic Threshold Low

Input Current for Logic High

Mode Control Response Time

Turn-On Response Time

Turn-Off Response Time

1.34

1.30

0.1

430

2.8

6.8

V

V

μ

A

ns

μ

s

μ

s

CDMA/FM Pin High Selects CDMA, Low Selects FM

PD1 and PD2 Pins Low Select IC ON, High Selects IC OFF

To 200

μ

A Supply Current

LOW DROPOUT REGULATOR

External PNP Pass Transistor, VCE

SAT

= –0.4 V Max

h

FE

= 100/300 Min/Max

Input Range

Nominal Output

Voltage Drop

Reference Output

2.9

4.2

2.70

200

1.23

V

V

mV

V

POWER SUPPLY

Supply Range Using Internal LDO

Supply Range Bypassing Internal LDO

Supply Current

Standby Current

Supply Input at Pin LDOE

Supply Input at Pins DVCC, IFVCC, LDOC

VGAIN = 1.5 V

2.9–5.0

2.7–3.6

10

0.78

V

V

mA

μ

A

OPERATING TEMPERATURE

T

MIN

to T

MAX

–40

+85

°

C

Specifications subject to change without notice.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6121 | CDMA 3 V Receiver IF Subsystem with Integrated Voltage Regulator |

| AD6121ACPRL | CDMA 3 V Receiver IF Subsystem with Integrated Voltage Regulator |

| AD6122ARSRL | CDMA 3 V Transmitter IF Subsystem with Integrated Voltage Regulator |

| AD6122ARS | CDMA 3 V Transmitter IF Subsystem with Integrated Voltage Regulator |

| AD6122ACP | CAP 39000UF 35V ELECT THA SERIES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6121ARSRL | 制造商:AD 制造商全稱:Analog Devices 功能描述:CDMA 3 V Receiver IF Subsystem with Integrated Voltage Regulator |

| AD6122 | 制造商:AD 制造商全稱:Analog Devices 功能描述:CDMA 3 V Transmitter IF Subsystem with Integrated Voltage Regulator |

| AD6122ACP | 制造商:Analog Devices 功能描述:COMMUNICATION CDMA 3V TRANSMITTER IF SUBSYSTEM 28SSOP |

| AD6122ACPRL | 制造商:AD 制造商全稱:Analog Devices 功能描述:CDMA 3 V Transmitter IF Subsystem with Integrated Voltage Regulator |

| AD6122ARS | 制造商:AD 制造商全稱:Analog Devices 功能描述:CDMA 3 V Transmitter IF Subsystem with Integrated Voltage Regulator |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。