- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375233 > AD5346BCP-REEL (ANALOG DEVICES INC) 2.5 V to 5.5 V, Parallel Interface 2.5 V to 5.5 V, Parallel Interface PDF資料下載

參數(shù)資料

| 型號(hào): | AD5346BCP-REEL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | 2.5 V to 5.5 V, Parallel Interface 2.5 V to 5.5 V, Parallel Interface |

| 中文描述: | PARALLEL, 8 BITS INPUT LOADING, 6 us SETTLING TIME, 8-BIT DAC, QCC40 |

| 封裝: | 6 X 6 MM, MO-220-VJJD-2, LFCSP-40 |

| 文件頁(yè)數(shù): | 14/24頁(yè) |

| 文件大?。?/td> | 949K |

| 代理商: | AD5346BCP-REEL |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

AD5346/AD5347/AD5348

Rev. 0 | Page 14 of 24

SUPPLY VOLTAGE

(V)

I

D

1.4

1.2

0

2.5

3.5

3.0

4.0

0.4

0.8

4.5

5.0

5.5

0.2

0.6

1.0

0

T

A

= +105

°

C

T

A

= +25

°

C

T

A

= –40

°

C

V

= 2V

GAIN = 1 UNBUFFERED

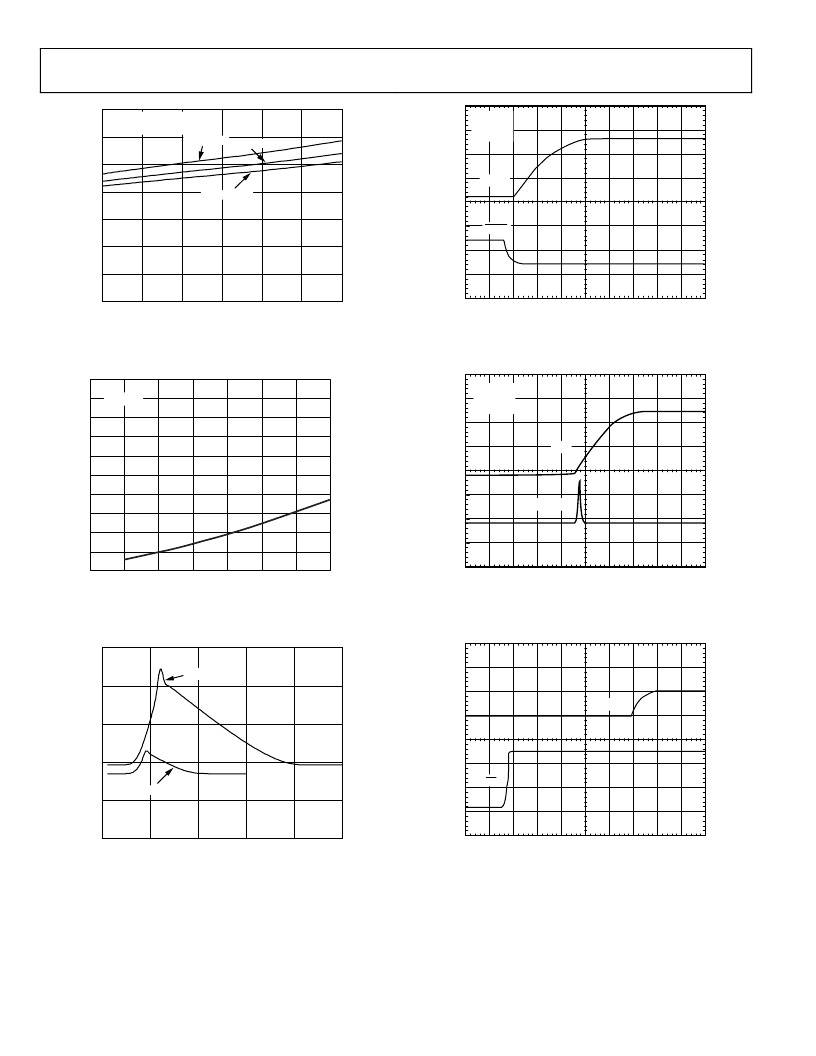

Figure 26. Supply Current vs. Supply Voltage

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

I

D

μ

A

T

A

= 25°C

2.0

2.5

3.0

3.5

4.0

4.5

5.0

5.5

V

DD

(V)

0

Figure 27. Power-Down Current vs. Supply Voltage

VLOGIC

(V)

I

D

2.5

0

0

3

2

1

4

1.5

5

0.5

1.0

2.0

0

T

A

= 25

°

C

V

DD

= 5V

V

DD

= 3V

Figure 28. Supply Current vs. Logic Input Voltage

CH2

CH1

V

OUT

A

T

A

= 25°C

V

DD

= 5V

V

REF

= 5V

0

CH1 1V, CH2 5V, TIME BASE = 1

μ

s/DIV

LDAC

Figure 29. Half-Scale Settling ( to Scale Code)

CH2

CH1

CH1 2V, CH2 200mV, TIME BASE = 200

μ

s/DIV

V

OUT

A

V

DD

0

T

A

= 25°C

V

DD

= 5V

V

REF

= 2V

Figure 30. Power-On Reset to 0 V

CH1

CH2

CH1 2.00V, CH2 1.00V, TIME BASE = 20

μ

s/DIV

V

OUT

1

0

PD

Figure 31. Exiting Power-Down to Midscale

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。