- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362070 > ACT-700SC-250F24C Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | ACT-700SC-250F24C |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁(yè)數(shù): | 21/24頁(yè) |

| 文件大小: | 227K |

| 代理商: | ACT-700SC-250F24C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

Aeroflex Circuit Technology

SCD7000 REV A 3/16/00 Plainview NY (516) 694-6700

21

For additional Detail Information regarding the operation of the Quantum Effect Devices (QED) RISCMark

RM7000

, 64-Bit Superscalar Microprocessor see the latest QED datasheet and users guide

(www.qedinc.com).

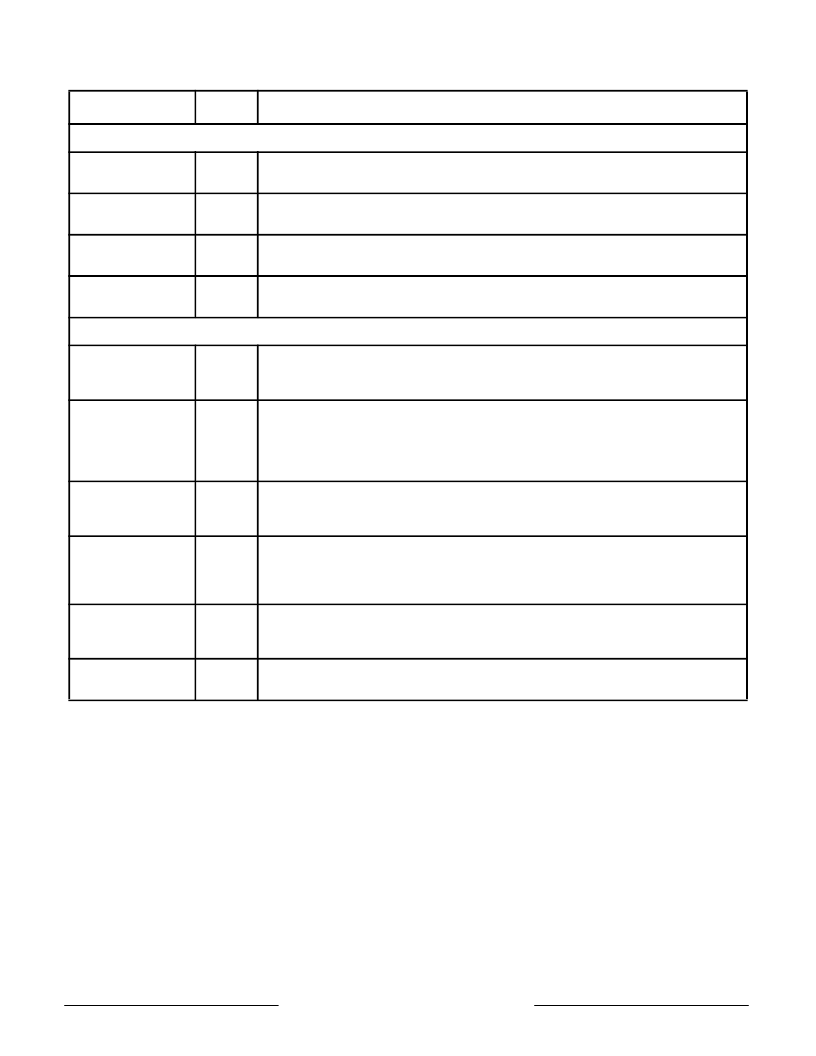

JTAG interface:

JTDI

Input

JTAG data in

JTAG serial data in.

JTCK

Input

JTAG clock input

JTAG serial clock input.

JTDO

Output

JTAG data out

JTAG serial data out.

JTMS

Input

JTAG command

JTAG command signal, signals that the incoming serial data is command data.

Initialization Interface:

BigEndian

Input

Big Endian / Little Endian Control

Allows the system to change the processor addressing mode without rewriting

the mode ROM.

VccOK

Input

Vcc is OK

When asserted, this signal indicates to the ACT 7000 that the 2.5V power supply

has been above 2.25V for more than 100 milliseconds and will remain stable.

The assertion of VccOK initiates the reading of the boot-time mode control serial

stream.

ColdReset*

Input

Cold Reset

This signal must be asserted for a power on reset or a cold reset. ColdReset

must be de-asserted synchronously with SysClock.

Reset*

Input

Reset

This signal must be asserted for any reset sequence. It may be asserted

synchronously or asynchronously for a cold reset, or synchronously to initiate a

warm reset. Reset must be de-asserted synchronously with SysClock.

ModeClock

Output

Boot Mode Clock

Serial boot-mode data clock output at the system clock frequency divided by two

hundred and fifty six.

ModeIn

Input

Boot Mode Data In

Serial boot-mode data input.

Pin Descriptions (Cont.)

The following is a list of control, data, clock, interrupt, and miscellaneous pins of the ACT 7000SC.

Pin Name

Type

Description

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACT-700SC-250F24I | Microprocessor |

| ACT-700SC-150F17C | Microprocessor |

| ACT-700SC-150F17I | Microprocessor |

| ACT-700SC-150F17M | Microprocessor |

| ACT-700SC-150F17Q | Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACT-700SC-250F24I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-250F24M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-250F24Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-250F24T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-266F17C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。