- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362070 > ACT-700SC-240F17I Microprocessor PDF資料下載

參數(shù)資料

| 型號: | ACT-700SC-240F17I |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數(shù): | 16/24頁 |

| 文件大小: | 227K |

| 代理商: | ACT-700SC-240F17I |

Aeroflex Circuit Technology

SCD7000 REV A 3/16/00 Plainview NY (516) 694-6700

16

kept in a low cost EPROM; alternatively the twenty or

so bits could be generated by the system interface

ASIC.

Immediately after the

VccOK

signal is asserted, the

processor reads a serial bit stream of 256 bits to

initialize all the fundamental operational modes.

ModeClock

runs continuously from the assertion of

VccO

K.

Boot-Time Modes

The boot-time serial mode stream is defined in

Table 16. Bit 0 is the bit presented to the processor

when

VccOK

is deasserted; bit 255 is the last.

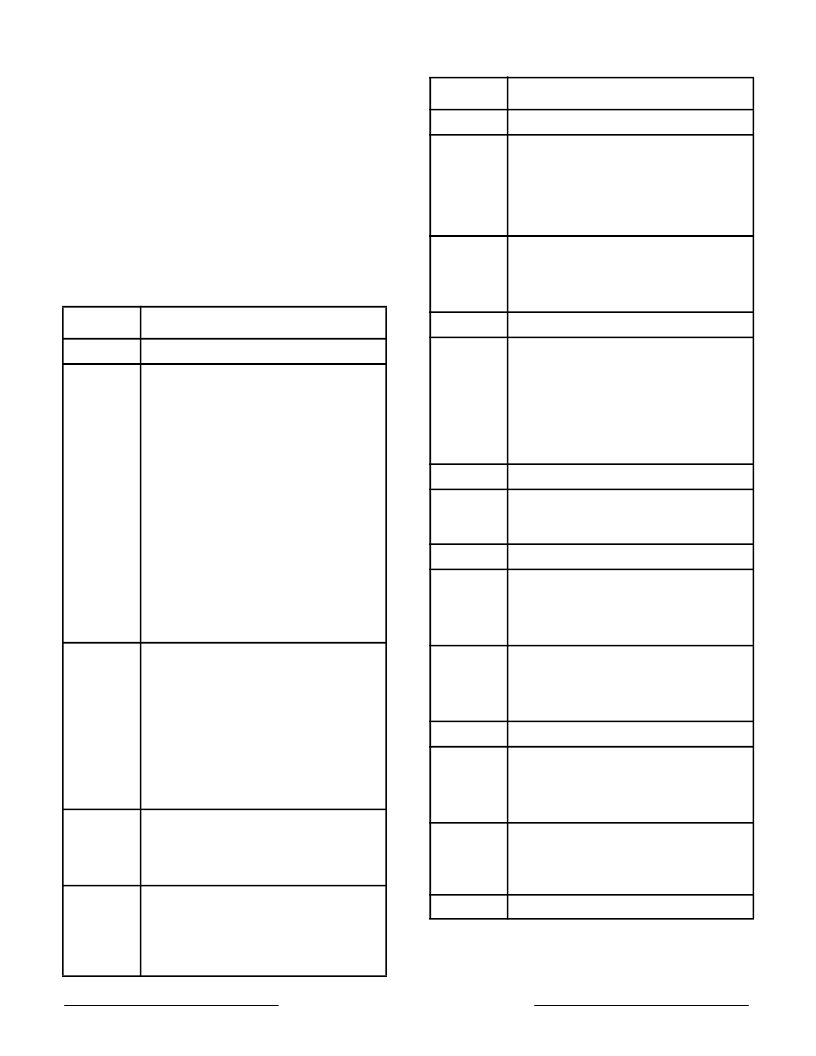

Table 16 – Boot Time Mode Stream

Mode bit

Description

0

Reserved: Must be zero

4..1

Write-back data rate

0:

DDDD

1:

DDxDDx

2:

DDxxDDxx

3:

DxDxDxDx

4:

DDxxxDDxxx

5

DDxxxxDDxxxx

6:

DxxDxxDxxDxx

7:

DDxxxxxxDDxxxxxx

8:

DxxxDxxxDxxxDxxx

9-15:Reserved

7..5

SysClock to Pclock Multiplier

Mode bit 20 = 0 / Mode bit 20 = 1

0:

Multiply by 2/x

1: Multiply by 3/x

2: Multiply by 4/x

3: Multiply by 5/2.5

4: Multiply by 6/x

5: Multiply by 7/3.5

6: Multiply by 8/x

7: Multiply by 9/4.5

8

Specifies byte ordering. Logically ORed

with BigEndian input signal.

0:

Little endian

1: Big endian

10..9

Non-Block Write Control

00: R4000 compatible non-block writes

01: Reserved

10: pipelined non-block writes

11: non-block write re-issue

11

Timer Interrupt Enable/Disable

0: Enable the timer interrupt on IP[5]

1: Disable the timer interrupt on IP[5]

12

Reserved: Must be zero

14..13

Output driver strength - 100% = fastest

00: 67% strength

01: 50% strength

10: 100% strength

11: 83% strength

15

Reserved must be zero

17..16

System configuration identifiers -

software visible in processor

Config[21..20] register

19..18

Reserved: Must be zero

20

Pclock to SysClock multipliers.

0: Integer multipliers (2,3,4,5,6,7,8,9)

1:

Half integer multipliers (2.5,3.5,4.5)

21

External Bus Width.

0: 64-bit

1: 32-bit

23..22

Reserved: Must be zero

24

JTLB Size.

0: 48 dual-entry

1:

64 dual-entry

25

On-chip secondary cache control.

0: Disable

1: Enable

255..26

Reserved: Must be zero

Table 16 – Boot Time Mode Stream (Cont.)

Mode bit

Description

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACT-700SC-240F17M | Microprocessor |

| ACT-700SC-240F17Q | Microprocessor |

| ACT-700SC-240F17T | Microprocessor |

| ACT-700SC-240F24C | Microprocessor |

| ACT-700SC-240F24I | Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACT-700SC-240F17M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-240F17Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-240F17T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-240F24C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-240F24I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。