- 您現在的位置:買賣IC網 > PDF目錄362070 > ACT-700SC-200F17I Microprocessor PDF資料下載

參數資料

| 型號: | ACT-700SC-200F17I |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數: | 5/24頁 |

| 文件大小: | 227K |

| 代理商: | ACT-700SC-200F17I |

Aeroflex Circuit Technology

SCD7000 REV A 3/16/00 Plainview NY (516) 694-6700

5

By pipelining the multiply-accumulate function and

dynamically determining the size of the input

operands, the ACT 7000SC is able to maximize

throughput while still using an area efficient

implementation.

Floating-Point Coprocessor

The ACT 7000SC incorporates a high-performance

fully pipe-lined floating-point coprocessor which

includes a floating-point register file and autonomous

execution units for multiply/ add/convert and

divide/square root. The floating-point coprocessor is a

tightly coupled co-execution unit, decoding and

executing instructions in parallel with, and in the case

of floating-point loads and stores, in cooperation with

the M pipe of the integer unit. As described earlier, the

superscalar capabilities of the ACT 7000SC allow

floating-point computation instructions to issue

concurrently with integer instructions.

Floating-Point Unit

The ACT 7000SC floating-point execution unit

supports single and double precision arithmetic, as

specified in the IEEE Standard 754. The execution

unit is broken into a separate divide/square root unit

and a pipelined multiply/add unit. Overlap of

divide/square root and multiply/add is supported.

The

ACT 7000SC

maintains

floating-point

exceptions

overlapped and pipelined operations. Precise

exceptions are extremely important in object-oriented

programming environments and highly desirable for

debugging in any environment.

The floating-point unit’s operation set includes

floating-point add, subtract, multiply, multiply-add,

divide, square root, reciprocal, reciprocal square root,

conditional moves, conversion between fixed-point

and floating-point format, conversion between

floating-point formats, and floating-point compare.

Table 5 gives the latencies of the floating-point

instructions in internal processor cycles.

fully

allowing

precise

both

while

Floating-Point General Register File

The floating-point general register file, FGR, is

made up of thirty-two 64-bit registers. With the

floating-point load and store double instructions,

LDC1 and SDC1, the floating-point unit can take

advantage of the 64-bit wide data cache and issue a

floating-point coprocessor load or store double-word

instruction in every cycle.

The floating-point control register file contains two

registers; one for determining configuration and

revision information for the coprocessor and one for

control and status information. These registers are

primarily used for diagnostic software, exception

handling, state saving and restoring, and control of

rounding modes.

To support superscalar operations, the FGR has

four read ports and two write ports, and is fully

bypassed to minimize operation latency in the

pipeline. Three of the read ports and one write port

are used to support the combined multiply-add

instruction while the fourth read and second write port

allows a concurrent floating-point load or store and

conditional moves.

System Control Coprocessor (CP0)

The system control coprocessor (CP0) in the MIPS

architecture is responsible for the virtual memory

sub-system, the exception control system, and the

diagnostics capability of the processor. In the MIPS

architecture, the system control coprocessor (and

thus the kernel software) is implementation

dependent. For memory management, the ACT

7000SC CP0 is logically identical to that of the

RM5200 Family and R5000. For interrupt exceptions

and diagnostics, the ACT 7000SC is a superset of the

RM5200 Family and R5000 implementing additional

features described later in the sections on Interrupts,

the Test/Breakpoint facility, and the Performance

Counter facility.

The memory management unit controls the virtual

memory system page mapping. It consists of an

instruction address translation buffer, or ITLB, a data

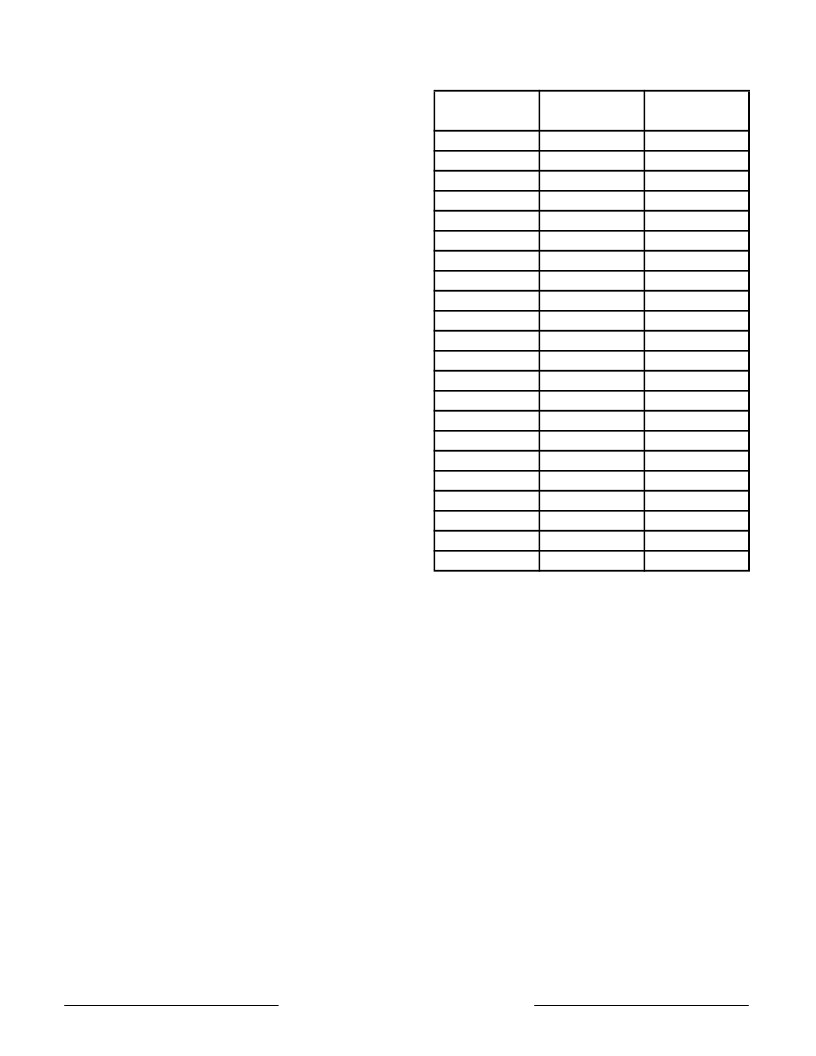

Table 5 – Floating Point Latencies and

Repeat Rates

Operation

Latency

single/double

Repeat Rate

single/double

fadd

4

1

fsub

4

1

fmult

4/5

1/2

fmadd

4/5

1/2

fmsub

4/5

1/2

fdiv

21/36

19/34

fsqrt

21/36

19/34

frecip

21/36

19/34

frsqrt

38/68

36/66

fcvt.s.d

4

1

fcvt.s.w

6

3

fcvt.s.l

6

3

fcvt.d.s

4

1

fcvt.d.w

4

1

fcvt.d.l

4

1

fcvt.w.s

4

1

fcvt.w.d

4

1

fcvt.l.s

4

1

fcvt.l.d

4

1

fcmp

1

1

fmov, fmovc

1

1

fabs, fneg

1

1

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相關PDF資料 |

PDF描述 |

|---|---|

| ACT-700SC-200F17M | Microprocessor |

| ACT-700SC-200F17Q | Microprocessor |

| ACT-700SC-200F17T | Microprocessor |

| ACT-700SC-200F24C | Microprocessor |

| ACT-700SC-200F24I | Microprocessor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ACT-700SC-200F17M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-200F17Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-200F17T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-200F24C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-200F24I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復。