- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362070 > ACT-700SC-150F24C Microprocessor PDF資料下載

參數(shù)資料

| 型號: | ACT-700SC-150F24C |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數(shù): | 12/24頁 |

| 文件大小: | 227K |

| 代理商: | ACT-700SC-150F24C |

Aeroflex Circuit Technology

SCD7000 REV A 3/16/00 Plainview NY (516) 694-6700

12

transaction. The ACT 7000SC samples these signals

before deasserting the address on read and write

requests.

ExtRqst*

and

Release*

are used to transfer control

of the SysAD and SysCmd buses from the processor

to an external device. When an external device needs

to control the interface, it asserts

ExtRqst

*. The ACT

7000SC responds by asserting

Release*

to release

the system interface to slave state.

ValidOut*

and

ValidIn*

are used by the ACT

7000SC and the external device respectively to

indicate that there is a valid command or data on the

SysAD and SysCmd buses. The ACT 7000SC

asserts

ValidOut*

when it is driving these buses with

a valid command or data, and the external device

drives

ValidIn*

when it has control of the buses and is

driving a valid command or data.

System Interface Operation

The ACT 7000SC can issue read and write

requests to an external device, while an external

device can issue null and write requests to the ACT

7000SC.

For processor reads, the ACT 7000SC asserts

ValidOut* and simultaneously drives the address and

read command on the SysAD and SysCmd buses. If

the system interface has

RdRdy*

asserted, then the

processor tristates its drivers and releases the system

interface to slave state by asserting

Release

*. The

external device can then begin sending data to the

ACT 7000SC.

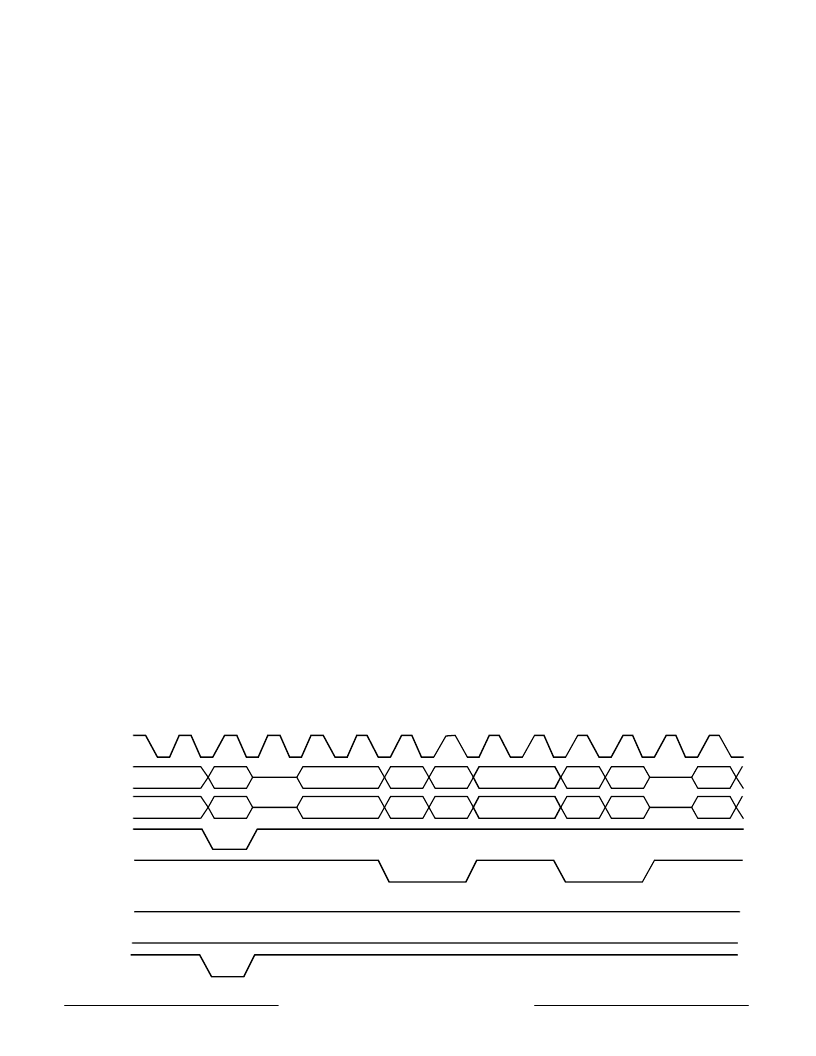

Figure 7 shows a processor block read request and

the external agent read response for a system with a

transaction.

The read latency is 4 cycles

(ValidOut*

to

ValidIn

*), and the response data pattern is DDxxDD.

Figure 9 shows a processor block write where the

processor was programmed with write-back data rate

boot code 2, or DDxxD-Dxx.

Data Prefetch

The ACT 7000SC is the first Aeroflex design to

support the MIPS IV integer data prefetch (PREF) and

floating-point data prefetch (PREFX) instructions.

These instructions are used by the compiler or by an

assembly language programmer when it is known or

suspected that an upcoming data reference is going

to miss in the cache. By appropriately placing a

prefetch instruction, the memory latency can be

hidden under the execution of other instructions. If the

execution of a prefetch instruction would cause a

memory management or address error exception the

prefetch is treated as a NOP.

The “Hint” field of the data prefetch instruction is

used to specify the action taken by the instruction.

The instruction can operate normally (that is, fetching

data as if for a load operation) or it can allocate and fill

a cache line with zeroes on a primary data cache

miss.

Enhanced Write Modes

The ACT 7000SC implements two enhancements

to the original R4000 write mechanism: Write Reissue

and Pipeline Writes. In write reissue mode, a write

rate of one write every two bus cycles can be

achieved. A write issues if

WrRdy*

is asserted two

cycles earlier and is still asserted during the issue

cycle. If it is not still asserted then the last write will

reissue. Pipe-lined writes have the same two bus

cycle write repeat rate, but can issue one additional

write following the deassertion of

WrRdy

*.

External Requests

The ACT 7000SC can respond to certain requests

issued by an external device. These requests take

one of two forms: Write requests and Null requests.

An external device executes a write request when it

wishes to update one of the processors writable

resources such as the internal interrupt register. A null

request is executed when the external device wishes

the processor to reassert ownership of the processor

external interface. Typically a null request will be

executed after an external device, that has acquired

control of the processor interface via

ExtRqst

*, has

Data0

nData

Data1

nData

Addr

Read

SysAD

SysCmd

ValidOut*

ValidIn*

RdRdy*

WrRdy*

Release*

SysClock

Data2

Data3

nData NEOD

Figure 7 – Processor Block Read

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACT-700SC-150F24I | Microprocessor |

| ACT-700SC-150F24M | Microprocessor |

| ACT-700SC-150F24Q | Microprocessor |

| ACT-700SC-150F24T | Microprocessor |

| ACT-700SC-200F17C | Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACT-700SC-150F24I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-150F24M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-150F24Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-150F24T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| ACT-700SC-200F17C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復。