- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4387 > A54SX32-2BG329 (Microsemi SoC)IC FPGA SX 48K GATES 329-BGA PDF資料下載

參數(shù)資料

| 型號: | A54SX32-2BG329 |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 56/64頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SX 48K GATES 329-BGA |

| 標準包裝: | 27 |

| 系列: | SX |

| LAB/CLB數(shù): | 2880 |

| 輸入/輸出數(shù): | 249 |

| 門數(shù): | 48000 |

| 電源電壓: | 3 V ~ 3.6 V,4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 329-BBGA |

| 供應(yīng)商設(shè)備封裝: | 329-PBGA(31x31) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當前第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

SX Family FPGAs

1- 2

v3.2

The R-cell contains a flip-flop featuring asynchronous

clear, asynchronous preset, and clock enable (using the

S0 and S1 lines) control signals (Figure 1-2). The R-cell

registers feature programmable clock polarity selectable

on a register-by-register basis. This provides additional

flexibility

while

allowing

mapping

of

synthesized

functions into the SX FPGA. The clock source for the

R-cell can be chosen from either the hardwired clock or

the routed clock.

The C-cell implements a range of combinatorial functions

up to 5-inputs (Figure 1-3 on page 1-3). Inclusion of the

DB input and its associated inverter function dramatically

increases the number of combinatorial functions that can

be implemented in a single module from 800 options in

previous architectures to more than 4,000 in the SX

architecture. An example of the improved flexibility

enabled by the inversion capability is the ability to

integrate a 3-input exclusive-OR function into a single

C-cell. This facilitates construction of 9-bit parity-tree

functions with 2 ns propagation delays. At the same

time, the C-cell structure is extremely synthesis friendly,

simplifying the overall design and reducing synthesis

time.

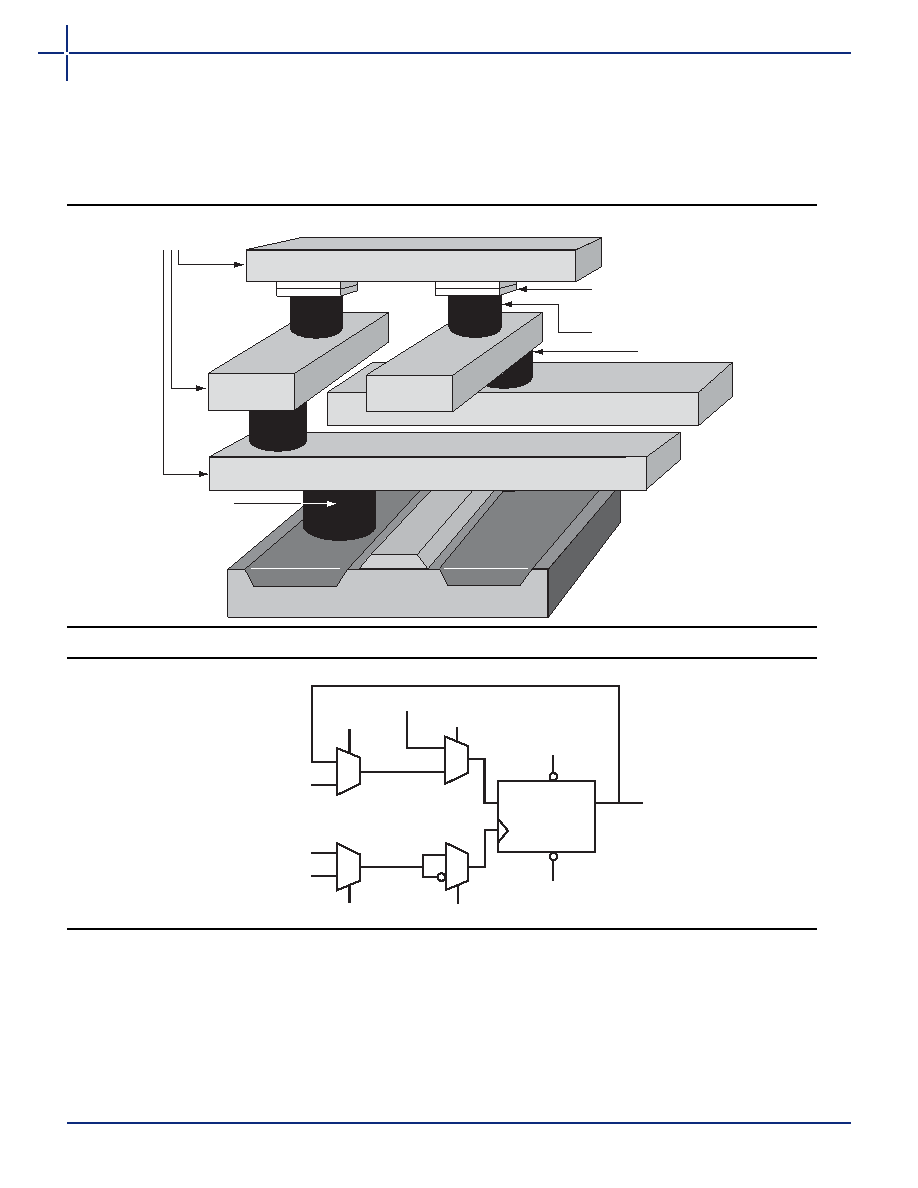

Figure 1-1

SX Family Interconnect Elements

Figure 1-2

R-Cell

Silicon Substrate

Tungsten Plug

Contact

Metal 1

Metal 2

Metal 3

Routing Tracks

Amorphous Silicon/

Dielectric Antifuse

Tungsten Plug Via

Direct

Connect

Input

CLKA, CLKB,

Internal Logic

HCLK

CKS

CKP

CLRB

PSETB

Y

DQ

Routed Data Input

S0

S1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BR24L64-W | IC EEPROM 64KBIT 400KHZ 8DIP |

| APA600-PQ208 | IC FPGA PROASIC+ 600K 208-PQFP |

| AT25128B-XHL-B | IC EEPROM 128KBIT 20MHZ 8TSSOP |

| APA600-PQG208 | IC FPGA PROASIC+ 600K 208-PQFP |

| M1AFS1500-1FG676 | IC FPGA 8MB FLASH 1.5M 676-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A54SX32-2BG329I | 功能描述:IC FPGA SX 48K GATES 329-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標準包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A54SX32-2BG329IX3 | 制造商:Microsemi Corporation 功能描述:FPGA SX Family 32K Gates 1800 Cells 320MHz 0.35um Technology 3.3V/5V 329-Pin BGA 制造商:Microsemi Corporation 功能描述:54SX 32K GATES 1800 MC 320MHZ IND CMOS 3.3/5V 329 BGA - Trays |

| A54SX32-2BGG329 | 功能描述:IC FPGA SX 48K GATES 329-BGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標準包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A54SX32-2BGG329I | 功能描述:IC FPGA SX 48K GATES 329-BGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標準包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A54SX322PQ208 | 制造商:ACTEL 功能描述:New |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。