- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379550 > A54SX16A-PQ208B (Electronic Theatre Controls, Inc.) LM136-5.0/LM236-5.0/LM336-5.0 5.0V Reference Diode; Package: TO-46; No of Pins: 3; Qty per Container: 1000; Container: Box PDF資料下載

參數(shù)資料

| 型號: | A54SX16A-PQ208B |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | LM136-5.0/LM236-5.0/LM336-5.0 5.0V Reference Diode; Package: TO-46; No of Pins: 3; Qty per Container: 1000; Container: Box |

| 中文描述: | 的SX - A系列FPGA的 |

| 文件頁數(shù): | 72/108頁 |

| 文件大?。?/td> | 720K |

| 代理商: | A54SX16A-PQ208B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁當前第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

SX-A Family FPGAs

2-52

v5.1

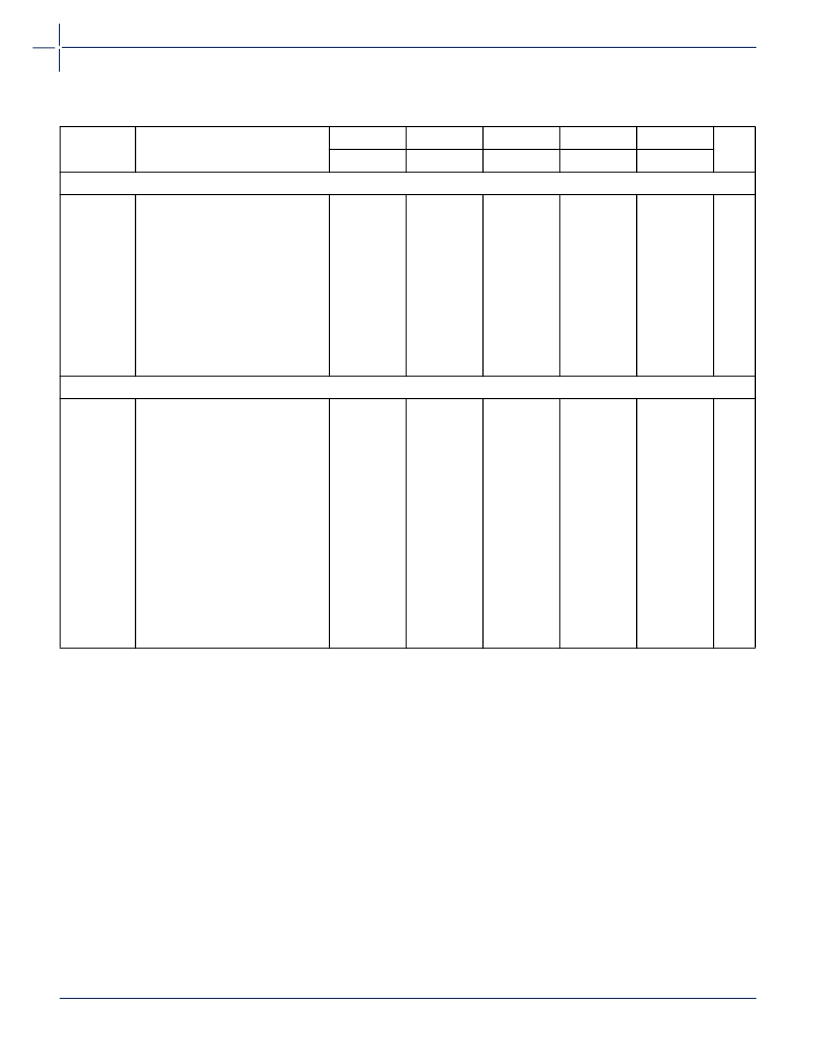

Table 2-41

A54SX72A Timing Characteristics

(Worst-Case Commercial Conditions V

CCA

= 2.25 V, V

CCI

= 4.75 V, T

J

= 70°C)

Parameter

5 V PCI Output Module Timing

1

Description

–3 Speed

–2 Speed

–1 Speed

Std. Speed

–F Speed

Units

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

t

DLH

Data-to-Pad Low to High

2.7

3.1

3.5

4.1

5.7

ns

t

DHL

Data-to-Pad High to Low

3.4

3.9

4.4

5.1

7.2

ns

t

ENZL

Enable-to-Pad, Z to L

1.3

1.5

1.7

2.0

2.8

ns

t

ENZH

Enable-to-Pad, Z to H

2.7

3.1

3.5

4.1

5.7

ns

t

ENLZ

Enable-to-Pad, L to Z

3.0

3.5

3.9

4.6

6.4

ns

t

ENHZ

d

TLH2

d

THL2

5 V TTL Output Module Timing

3

Enable-to-Pad, H to Z

3.4

3.9

4.4

5.1

7.2

ns

Delta Low to High

0.016

0.016

0.02

0.022

0.032

ns/pF

Delta High to Low

0.026

0.03

0.032

0.04

0.052

ns/pF

t

DLH

Data-to-Pad Low to High

2.4

2.8

3.1

3.7

5.1

ns

t

DHL

Data-to-Pad High to Low

3.1

3.5

4.0

4.7

6.6

ns

t

DHLS

Data-to-Pad High to Low—low slew

7.4

8.5

9.7

11.4

15.9

ns

t

ENZL

Enable-to-Pad, Z to L

2.1

2.4

2.7

3.2

4.5

ns

t

ENZLS

Enable-to-Pad, Z to L—low slew

7.4

8.4

9.5

11.0

15.4

ns

t

ENZH

Enable-to-Pad, Z to H

2.4

2.8

3.1

3.7

5.1

ns

t

ENLZ

Enable-to-Pad, L to Z

3.6

4.2

4.7

5.6

7.8

ns

t

ENHZ

d

TLH2

d

THL2

d

THLS2

Enable-to-Pad, H to Z

3.1

3.5

4.0

4.7

6.6

ns

Delta Low to High

0.014

0.017

0.017

0.023

0.031

ns/pF

Delta High to Low

0.023

0.029

0.031

0.037

0.051

ns/pF

Delta High to Low—low slew

0.043

0.046

0.057

0.066

0.089

ns/pF

Notes:

1. Delays based on 50 pF loading.

2. To obtain the slew rate, substitute the appropriate Delta value, load capacitance, and the V

CCI

value into the following equation:

Slew Rate [V/ns] = (0.1*V

CCI

– 0.9*V

CCI)

/ (C

load

* d

T[LH|HL|HLS]

)

where C

load

is the load capacitance driven by the I/O in pF

d

T[LH|HL|HLS]

is the worst case delta value from the datasheet in ns/pF.

3. Delays based on 35 pF loading.

相關PDF資料 |

PDF描述 |

|---|---|

| A54SX16A-PQ208I | sx-a family FPGAS |

| A54SX16A-PQ208M | SX-A FAMILY FPGAs |

| A54SX16A-TQ208 | LM2423 220V Monolithic Triple Channel 15 MHz CRT DTV Driver; Package: TO-220; No of Pins: 11 |

| A54SX16A-TQ208A | SX-A Family FPGAs |

| A54SX16A-TQ208B | SX-A Family FPGAs |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| A54SX16A-PQ208I | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX-A 標準包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計:36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

| A54SX16A-PQ208M | 制造商:Microsemi Corporation 功能描述:FPGA SX-A 16K GATES 924 CELLS 227MHZ 0.25UM/0.22UM 2.5V 208P - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA 175 I/O 208PQFP |

| A54SX16A-PQG208 | 功能描述:IC FPGA 180I/O 208PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX-A 標準包裝:24 系列:ECP2 LAB/CLB數(shù):1500 邏輯元件/單元數(shù):12000 RAM 位總計:226304 輸入/輸出數(shù):131 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:208-BFQFP 供應商設備封裝:208-PQFP(28x28) |

| A54SX16A-PQG208A | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX-A 標準包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計:36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

| A54SX16A-PQG208I | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX-A 標準包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計:36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

發(fā)布緊急采購,3分鐘左右您將得到回復。