- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379534 > A54SX16-2PL208PP (Actel Corporation) 54SX family FPGAs PDF資料下載

參數(shù)資料

| 型號: | A54SX16-2PL208PP |

| 廠商: | Actel Corporation |

| 元件分類: | FPGA |

| 英文描述: | 54SX family FPGAs |

| 中文描述: | 54SX家庭的FPGAs |

| 文件頁數(shù): | 24/57頁 |

| 文件大小: | 415K |

| 代理商: | A54SX16-2PL208PP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

5 4 S X F a m ily F P G A s

24

v3.1

T im ing C ha ra c t e ris t ic s

Timing characteristics for 54SX devices fall into three

categories:

family-dependent, device-dependent,

design-dependent.

The

input

characteristics are common to all 54SX family members.

Internal routing delays are device dependent. Design

dependency means actual delays are not determined until

after placement and routing of the user’s design is complete.

Delay values may then be determined by using the

DirectTime Analyzer utility or performing simulation with

post-layout delays.

and

and

output

buffer

C rit ic a l N e t s a nd T y pic a l N e t s

Propagation delays are expressed only for typical nets,

which are used for initial design performance evaluation.

Critical net delays can then be applied to the most

time-critical paths. Critical nets are determined by net

property assignment prior to placement and routing. Up to

6%of the nets in a design may be designated as critical,

while 90%of the nets in a design are typical.

L ong T ra c k s

Some nets in the design use long tracks. Long tracks are

special routing resources that span multiple rows, columns,

or modules. Long tracks employ three and sometimes five

antifuse connections. This increases capacitance and

resistance, resulting in longer net delays for macros

connected to long tracks. Typically up to 6%of nets in a fully

utilized device require long tracks. Long tracks contribute

approximately 4 ns to 8.4 ns delay. This additional delay is

represented statistically in higher fanout (FO=24) routing

delays in the data sheet specifications section.

T im ing De ra t ing

54SX devices are manufactured in a CMOS process.

Therefore, device performance varies according to

temperature, voltage, and process variations. Minimum

timing parameters reflect maximum operating voltage,

minimum operating temperature, and best-case processing.

Maximum timing parameters reflect minimum operating

voltage, maximum operating temperature, and worst-case

processing.

T e m pe ra t ure a nd V olt a g e De ra t ing F a c t ors

(Norma lize d to Wors t-C a s e C omme rc ia l, T

J

= 70

°

C , V

C C A

= 3.0V )

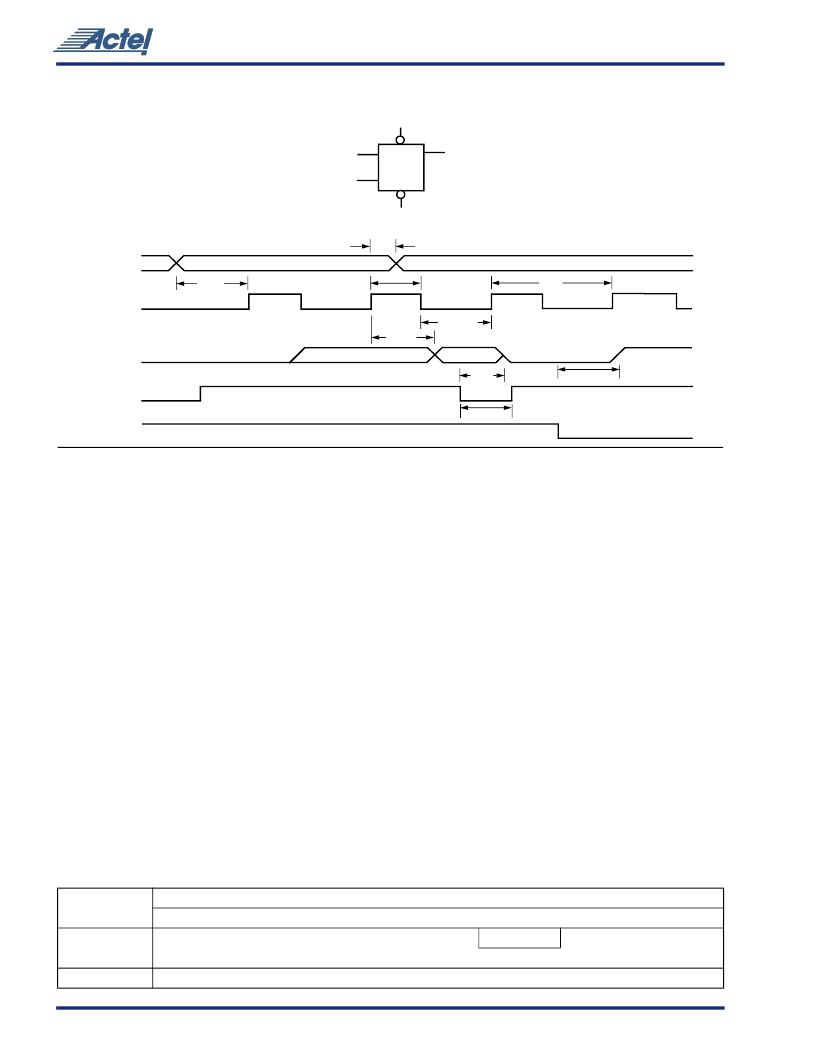

R e g is t e r C e ll T im ing C ha ra c t e ris t ic s

F lip-F lops

(Positive edge triggered)

D

CLK

CLR

Q

D

CLK

Q

CLR

t

HPWH

,

t

RPWH

t

WASYN

t

HD

t

SUD

t

HP

t

HPWL

,

t

RPWL

t

RCO

t

CLR

PRESET

t

PRESET

PRESET

V

CCA

3.0

3.3

3.6

Junction Temperature (T

J

)

25

–55

–40

0

70

85

125

0.75

0.70

0.66

0.78

0.73

0.69

0.87

0.82

0.77

0.89

0.83

0.78

1.00

0.93

0.87

1.04

0.97

0.92

1.16

1.08

1.02

相關PDF資料 |

PDF描述 |

|---|---|

| A54SX16-2PQ208 | 54SX Family FPGAs |

| A54SX16-2PQ208I | 54SX Family FPGAs |

| A54SX16-2PQ208M | 54SX family FPGAs |

| A54SX16-2PQ208PP | 54SX family FPGAs |

| A54SX16-2TQ208 | LM193/LM293/LM393/LM2903 Low Power Low Offset Voltage Dual Comparators; Package: CERDIP; No of Pins: 8; Qty per Container: 40; Container: Rail |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A54SX16-2PQ208 | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX 產(chǎn)品培訓模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標準包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應商設備封裝:484-FBGA(23x23) |

| A54SX16-2PQ208I | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX 產(chǎn)品培訓模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標準包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應商設備封裝:484-FBGA(23x23) |

| A54SX16-2PQG208 | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX 產(chǎn)品培訓模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標準包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應商設備封裝:484-FBGA(23x23) |

| A54SX16-2PQG208I | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX 產(chǎn)品培訓模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標準包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應商設備封裝:484-FBGA(23x23) |

| A54SX16-2TQ176 | 功能描述:IC FPGA SX 24K GATES 176-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:SX 產(chǎn)品培訓模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標準包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計:6635520 輸入/輸出數(shù):270 門數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應商設備封裝:484-FBGA(23x23) |

發(fā)布緊急采購,3分鐘左右您將得到回復。