- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄379528 > A54SX08P-1PL208I (Electronic Theatre Controls, Inc.) Circular Connector; MIL SPEC:MIL-DTL-38999 Series III; Body Material:Metal; Series:TVP00; Number of Contacts:128; Connector Shell Size:25; Connecting Termination:Crimp; Circular Shell Style:Wall Mount Receptacle; Body Style:Straight PDF資料下載

參數(shù)資料

| 型號(hào): | A54SX08P-1PL208I |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類(lèi): | 圓形連接器 |

| 英文描述: | Circular Connector; MIL SPEC:MIL-DTL-38999 Series III; Body Material:Metal; Series:TVP00; Number of Contacts:128; Connector Shell Size:25; Connecting Termination:Crimp; Circular Shell Style:Wall Mount Receptacle; Body Style:Straight |

| 中文描述: | 54SX家庭的FPGA |

| 文件頁(yè)數(shù): | 22/57頁(yè) |

| 文件大小: | 415K |

| 代理商: | A54SX08P-1PL208I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

5 4 S X F a m ily F P G A s

22

v3.1

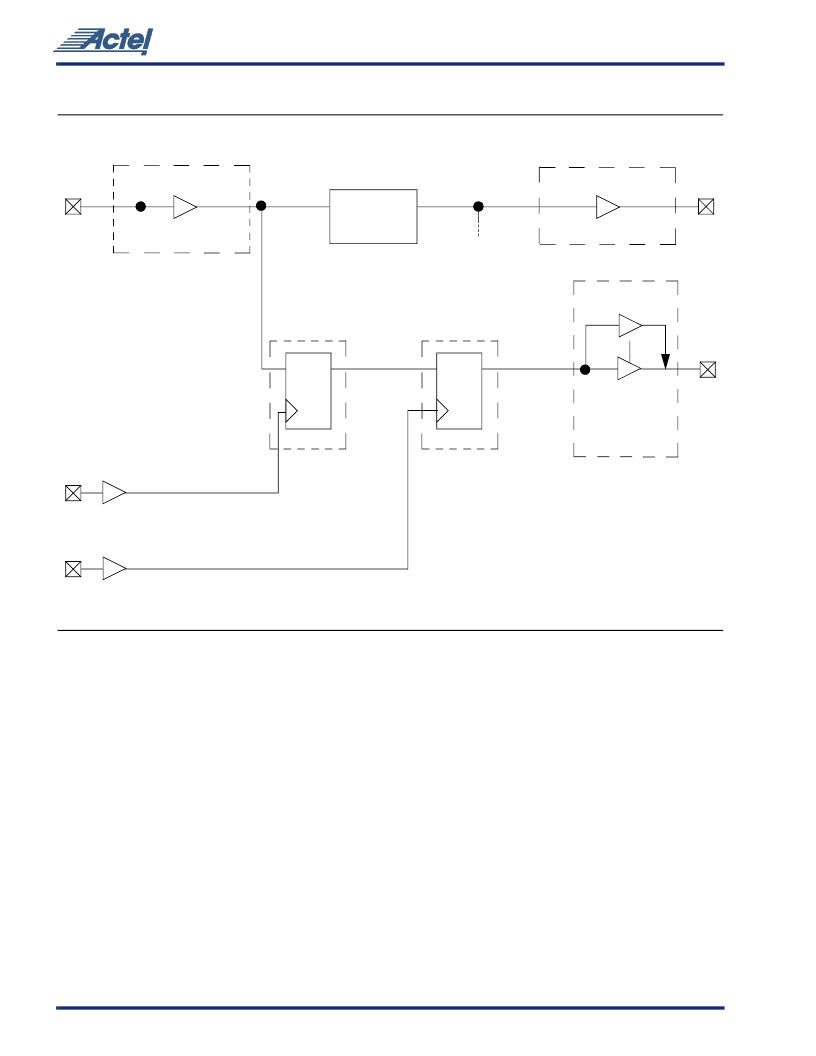

5 4 S X T im ing Mode l*

H a rd-W ire d C loc k

External Set-Up

= t

INY

+ t

IRD1

+ t

SUD

– t

HCKH

= 1.5 + 0.3 + 0.5 – 1.0 = 1.3 ns

Clock-to-Out (Pin-to-Pin)

= t

HCKH

+ t

RCO

+ t

RD1

+ t

DHL

= 1.0 + 0.8 + 0.3 + 1.6 = 3.7 ns

R out e d C loc k

External Set-Up = t

INY

+ t

IRD1

+ t

SUD

– t

RCKH

= 1.5 + 0.3 + 0.5 – 1.5 = 0.8 ns

Clock-to-Out (Pin-to-Pin)

= t

RCKH

+ t

RCO

+ t

RD1

+ t

DHL

= 1.52+ 0.8 + 0.3 + 1.6 = 4.2 ns

*Values shown for A54SX08-3, worst-case commercial conditions.

Output Delays

Internal Delays

Input Delays

Hard-Wired

Clock

I/O Module

F

HMAX

= 320 MHz

t

INY

= 1.5 ns

t

IRD2

= 0.6 ns

Combinatorial

Cell

t

PD

=0.6 ns

Register

Cell

I/O Module

t

RD1

= 0.3 ns

t

RD4

= 1.0 ns

t

RD8

= 1.9 ns

t

DHL

= 1.6 ns

I/O Module

Routed

Clock

F

MAX

= 250 MHz

D

Q

D

Q

t

DHL

= 1.6 ns

t

ENZH

= 2.3 ns

t

RD1

= 0.3 ns

t

RCO

= 0.8 ns

t

SUD

= 0.5 ns

t

HD

= 0.0 ns

Predicted

Routing

Delays

t

RCKH

= 1.5 ns (100% Load)

t

RD1

= 0.3 ns

Register

Cell

t

RCO

= 0.8 ns

t

HCKH

= 1.0 ns

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。