- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362024 > A42MX24-FPQ160 Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號(hào): | A42MX24-FPQ160 |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場(chǎng)可編程門陣列(FPGA) |

| 文件頁數(shù): | 10/116頁 |

| 文件大?。?/td> | 3110K |

| 代理商: | A42MX24-FPQ160 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁

40MX and 42MX FPGA Families

10

v5.0

Test Circuitry

All devices contain Actel

’

s ActionProbe test circuitry which

test and debug a design once it is programmed into a device.

Once a device has been programmed, the ActionProbe test

circuitry allows the designer to probe any internal node

during device operation to aid in debugging a design. In

addition, 42MX devices contain IEEE Standard 1149.1

boundary scan test circuitry.

IEEE Standard 1149.1 Boundary Scan Testing (BST)

IEEE Standard 1149.1 defines a four-pin Test Access Port

(TAP) interface for testing integrated circuits in a system.

The 42MX family provides five BST pins: Test Data In (TDI),

Test Data Out (TDO), Test Clock (TCK), and Test Mode

Select Test Reset (TRST) (42MX24A only). Devices are

configured in a test

“

chain

”

where BST data can be

transmitted serially between devices via TDO-to-TDI

interconnections. The TMS and TCK signals are shared

among all devices in the test chain so that all components

operate in the same state.

The 42MX family implements a subset of the IEEE Standard

1149.1 BST instruction in addition to a private instruction,

which allows the use of Actel

’

s ActionProbe facility with

BST. Refer to the IEEE Standard 1149.1 specification for

detailed information regarding BST.

Boundary Scan Circuitry

The 42MX boundary scan circuitry consists of a Test Access

Port (TAP) controller, test instruction register, a JPROBE

register, a bypass register, and a boundary scan register.

Figure 11 on page 11

shows a block diagram of the 42MX

boundary scan circuitry.

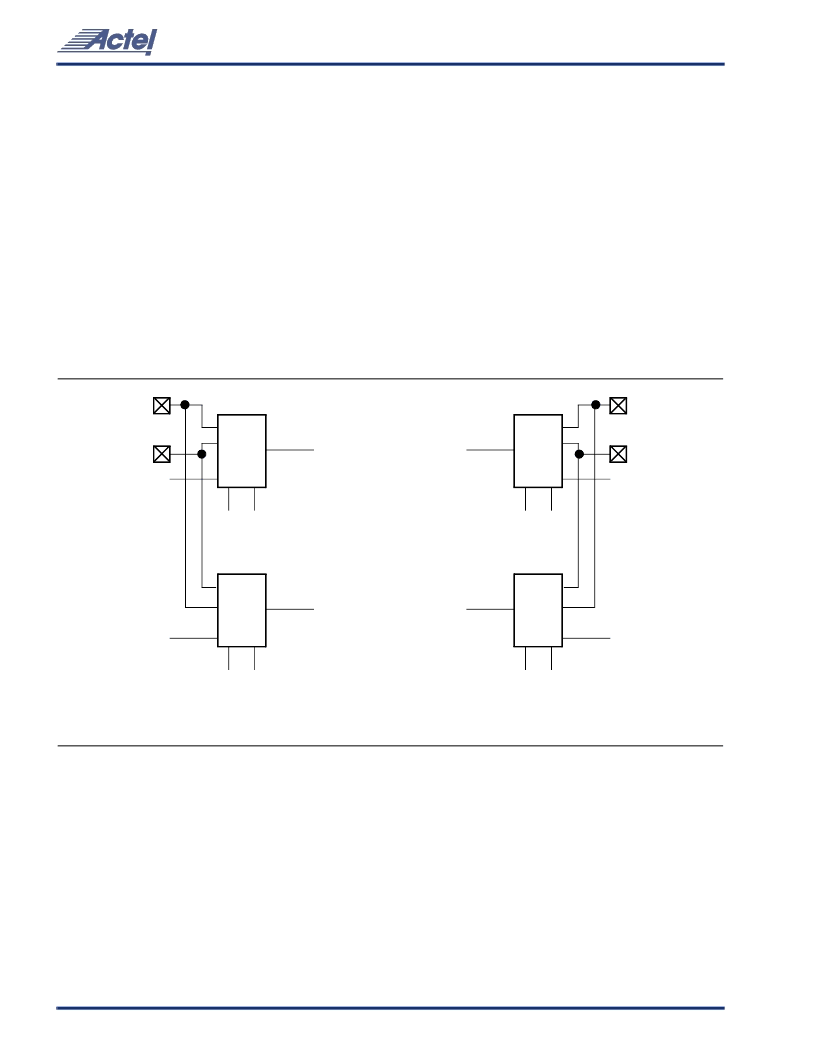

Figure 10

Quadrant Clock Network

Quad

Clock

Module

QCLKA

QCLKB

*QCLK1IN

S0 S1

QCLK1

Quad

Clock

Module

*QCLK2IN

S0 S1

QCLK2

Quad

Clock

Module

QCLKC

QCLKD

*QCLK3IN

S0

S1

QCLK3

Quad

Clock

Module

*QCLK4IN

S0

S1

QCLK4

*QCLK1IN, QCLK2IN, QCLK3IN, and QCLK4IN are internally-generated signals.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A42MX36-1BG272I | Field Programmable Gate Array (FPGA) |

| A42MX36-1BG272M | Field Programmable Gate Array (FPGA) |

| A42MX36-1CQ208 | Field Programmable Gate Array (FPGA) |

| A42MX36-1CQ208B | Field Programmable Gate Array (FPGA) |

| A42MX36-1CQ208M | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A42MX24-FPQ208 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:MX 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A42MX24-FPQG160 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:MX 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A42MX24-FPQG208 | 功能描述:IC FPGA MX SGL CHIP 36K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:MX 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A42MX24-FTQ176 | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:MX 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A42MX24-FTQG176 | 功能描述:IC FPGA MX SGL CHIP 36K 176-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:MX 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。