- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4443 > A42MX16-TQ176A (Microsemi SoC)IC FPGA MX SGL CHIP 24K 176-TQFP PDF資料下載

參數(shù)資料

| 型號: | A42MX16-TQ176A |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 93/142頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA MX SGL CHIP 24K 176-TQFP |

| 標準包裝: | 40 |

| 系列: | MX |

| 輸入/輸出數(shù): | 140 |

| 門數(shù): | 24000 |

| 電源電壓: | 3 V ~ 3.6 V,4.5 V ~ 5.5 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 125°C |

| 封裝/外殼: | 176-LQFP |

| 供應(yīng)商設(shè)備封裝: | 176-TQFP(24x24) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁當前第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁

40MX and 42MX FPGA Families

1- 50

R e v i sio n 1 1

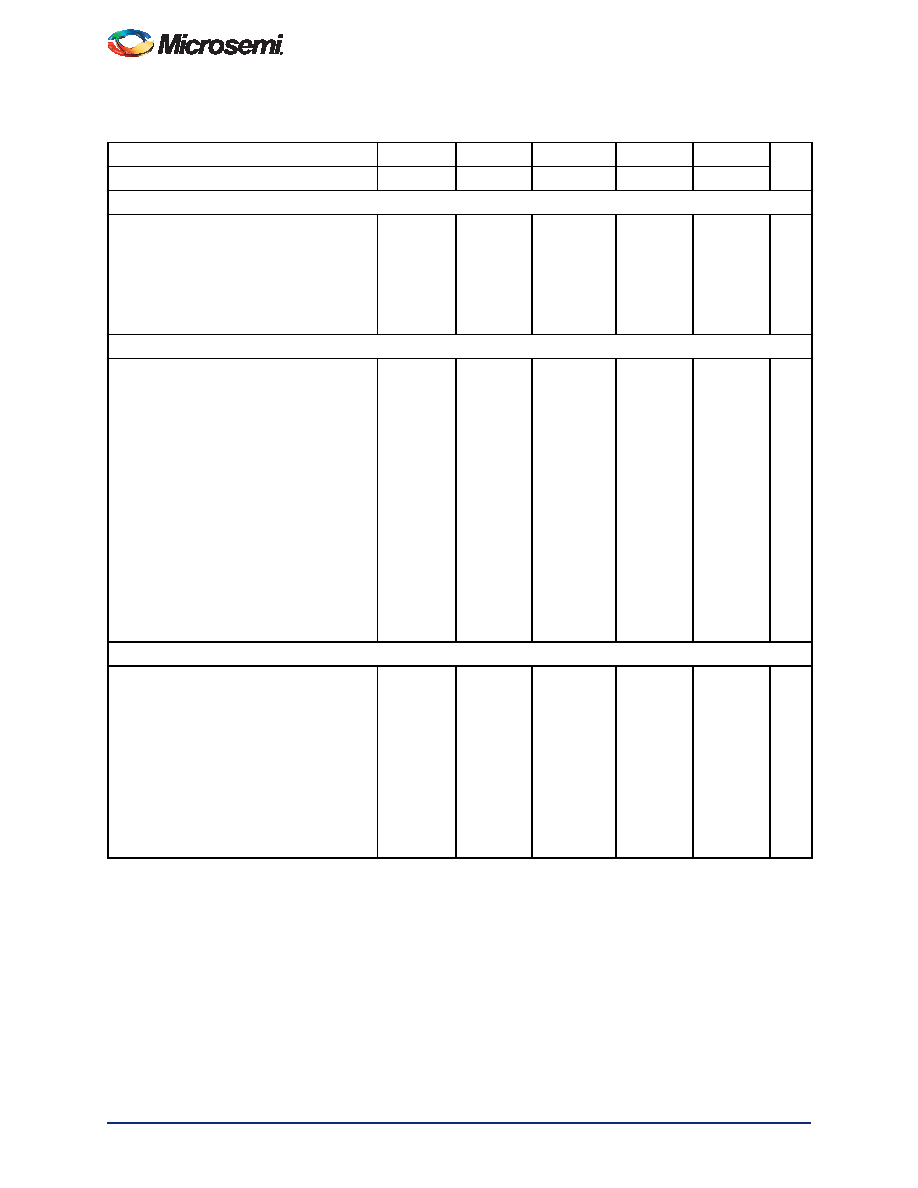

Input Module Predicted Routing Delays1

tIRD1

FO = 1 Routing Delay

2.9

3.3

3.8

4.5

6.3

ns

tIRD2

FO = 2 Routing Delay

3.6

4.2

4.8

5.6

7.8

ns

tIRD3

FO = 3 Routing Delay

4.4

5.0

5.7

6.7

9.4

ns

tIRD4

FO = 4 Routing Delay

5.1

5.9

6.7

7.8

11.0

ns

tIRD8

FO = 8 Routing Delay

8.0

9.3

10.5

12.4

17.2

ns

Global Clock Network

tCKH

Input LOW to HIGH

FO = 16

FO = 128

6.4

7.4

8.4

9.9

13.8

ns

tCKL

Input HIGH to LOW

FO = 16

FO = 128

6.8

7.8

8.9

10.4

14.6

ns

tPWH

Minimum Pulse

Width HIGH

FO = 16

FO = 128

3.1

3.3

3.6

3.8

4.1

4.3

4.8

5.1

6.7

7.1

ns

tPWL

Minimum Pulse

Width LOW

FO = 16

FO = 128

3.1

3.3

3.6

3.8

4.1

4.3

4.8

5.1

6.7

7.1

ns

tCKSW

Maximum Skew

FO = 16

FO = 128

0.6

0.8

0.6

0.9

0.7

1.0

0.8

1.2

1.6

ns

tP

Minimum Period

FO = 16

FO = 128

6.5

6.8

7.5

7.8

8.5

8.9

10.1

10.4

14.1

14.6

ns

fMAX

Maximum Frequency FO = 16

FO = 128

113

109

105

101

96

92

83

80

50

48

MHz

TTL Output Module Timing4

tDLH

Data-to-Pad HIGH

4.7

5.4

6.1

7.2

10.0

ns

tDHL

Data-to-Pad LOW

5.6

6.4

7.3

8.6

12.0

ns

tENZH

Enable Pad Z to HIGH

5.2

6.0

6.9

8.1

11.3

ns

tENZL

Enable Pad Z to LOW

6.6

7.6

8.6

10.1

14.1

ns

tENHZ

Enable Pad HIGH to Z

11.1

12.8

14.5

17.1

23.9

ns

tENLZ

Enable Pad LOW to Z

8.2

9.5

10.7

12.6

17.7

ns

dTLH

Delta LOW to HIGH

0.03

0.04

0.06

ns/pF

dTHL

Delta HIGH to LOW

0.04

0.05

0.06

0.08

ns/pF

Table 1-31 A40MX04 Timing Characteristics (Nominal 3.3 V Operation) (continued)

(Worst-Case Commercial Conditions, VCC = 3.0 V, TJ = 70°C)

–3 Speed

–2 Speed

–1 Speed

Std Speed

–F Speed

Units

Parameter / Description

Min. Max. Min. Max. Min.

Max. Min. Max. Min. Max.

Notes:

1. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for

estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

2. Set-up times assume fanout of 3. Further testing information can be obtained from the Timer utility.

3. The hold time for the DFME1A macro may be greater than 0 ns. Use the Timer tool from the Designer software to check

the hold time for this macro.

4. Delays based on 35 pF loading.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RSC28DTEH | CONN EDGECARD 56POS .100 EYELET |

| A42MX16-TQG176A | IC FPGA MX SGL CHIP 24K 176-TQFP |

| HMC40DRYS | CONN EDGECARD 80POS DIP .100 SLD |

| A54SX32A-2FG144 | IC FPGA SX 48K GATES 144-FBGA |

| HMC35DRAS | CONN EDGECARD 70POS R/A .100 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A42MX16-TQ176I | 功能描述:IC FPGA MX SGL CHIP 24K 176-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 標準包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A42MX16-TQ176M | 制造商:Microsemi Corporation 功能描述:FPGA 24K GATES 608 CELLS 103MHZ/172MHZ 0.45UM 3.3V/5V 176TQF - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA MX SGL CHIP 24K 176-TQFP 制造商:Microsemi Corporation 功能描述:IC FPGA 140 I/O 176TQFP |

| A42MX16-TQ208A | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:40MX and 42MX Automotive FPGA Families |

| A42MX16-TQG176 | 功能描述:IC FPGA 140I/O 176TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 標準包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計:221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| A42MX16-TQG176A | 功能描述:IC FPGA MX SGL CHIP 24K 176-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 標準包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。