- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄164974 > A40MX04-1PL44M FPGA, 547 CLBS, 6000 GATES, 92 MHz, PQCC44 PDF資料下載

參數(shù)資料

| 型號: | A40MX04-1PL44M |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 547 CLBS, 6000 GATES, 92 MHz, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 102/124頁 |

| 文件大小: | 3142K |

| 代理商: | A40MX04-1PL44M |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁當前第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁

40MX and 42MX FPGA Families

v6.1

1-73

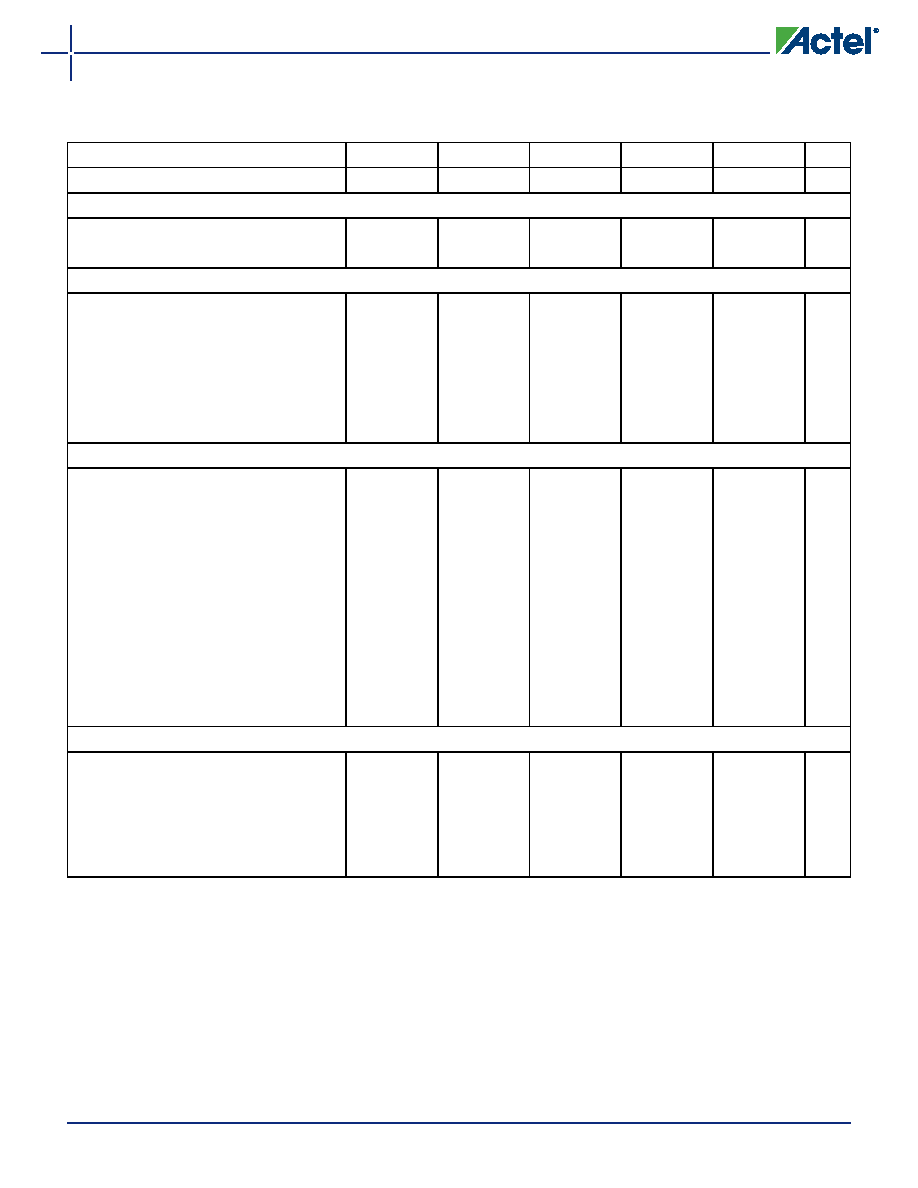

Table 39

A42MX36 Timing Characteristics (Nominal 3.3V Operation)

(Worst-Case Commercial Conditions, VCCA = 3.0V, TJ = 70°C)

‘–3’ Speed

‘–2’ Speed

‘–1’ Speed

‘Std’ Speed

‘–F’ Speed

Parameter Description

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max. Units

Logic Module Combinatorial Functions1

tPD

Internal Array Module Delay

1.9

2.1

2.3

2.7

3.8

ns

tPDD

Internal Decode Module Delay

2.2

2.5

2.8

3.3

4.7

ns

Logic Module Predicted Routing Delays2

tRD1

FO=1 Routing Delay

1.3

1.5

1.7

2.0

2.7

ns

tRD2

FO=2 Routing Delay

1.8

2.0

2.3

2.7

3.7

ns

tRD3

FO=3 Routing Delay

2.3

2.5

2.8

3.4

4.7

ns

tRD4

FO=4 Routing Delay

2.8

3.1

3.5

4.1

5.7

ns

tRD5

FO=8 Routing Delay

4.6

5.2

5.8

6.9

9.6

ns

tRDD

Decode-to-Output Routing Delay

0.5

0.6

0.7

1.0

ns

Logic Module Sequential Timing3, 4

tCO

Flip-Flop Clock-to-Output

1.8

2.0

2.3

2.7

3.7

ns

tGO

Latch Gate-to-Output

1.8

2.0

2.3

2.7

3.7

ns

tSUD

Flip-Flop (Latch) Set-Up Time

0.4

0.5

0.6

0.7

0.9

ns

tHD

Flip-Flop (Latch) Hold Time

0.0

ns

tRO

Flip-Flop (Latch) Reset-to-Output

2.2

2.4

2.7

3.2

4.5

ns

tSUENA

Flip-Flop (Latch) Enable Set-Up

1.0

1.1

1.2

1.4

2.0

ns

tHENA

Flip-Flop (Latch) Enable Hold

0.0

ns

tWCLKA

Flip-Flop (Latch) Clock Active

Pulse Width

4.6

5.2

5.8

6.9

9.6

ns

tWASYN

Flip-Flop (Latch) Asynchronous

Pulse Width

6.1

6.8

7.7

9.0

12.6

ns

Synchronous SRAM Operations

tRC

Read Cycle Time

9.5

10.5

11.9

14.0

19.6

ns

tWC

Write Cycle Time

9.5

10.5

11.9

14.0

19.6

ns

tRCKHL

Clock HIGH/LOW Time

4.8

5.3

6.0

7.0

9.8

ns

tRCO

Data Valid After Clock HIGH/LOW

4.8

5.3

6.0

7.0

9.8

ns

tADSU

Address/Data Set-Up Time

2.3

2.5

2.8

3.4

4.8

ns

Notes:

1. For dual-module macros, use tPD1 + tRD1 + tPDn, tCO + tRD1 + tPDn, or tPD1 + tRD1 + tSUD, whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating

device performance. Post-route timing analysis or simulation is required to determine actual performance.

3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be

obtained from the Timer utility.

4. Set-up and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/

hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to

the G input subtracts (adds) to the internal setup (hold) time.

5. Delays based on 35 pF loading.

相關PDF資料 |

PDF描述 |

|---|---|

| A40MX04-1PL44X79 | FPGA, 547 CLBS, 6000 GATES, 92 MHz, PQCC44 |

| A40MX04-1PL44 | FPGA, 547 CLBS, 6000 GATES, 92 MHz, PQCC44 |

| A40MX04-1PL68IX79 | FPGA, 547 CLBS, 6000 GATES, 92 MHz, PQCC68 |

| A40MX04-1PL68I | FPGA, 547 CLBS, 6000 GATES, 92 MHz, PQCC68 |

| A40MX04-1PL68MX79 | FPGA, 547 CLBS, 6000 GATES, 92 MHz, PQCC68 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| A40MX04-1PL44MX130 | 制造商:Microsemi Corporation 功能描述:FPGA 6K GATES 547 CELLS 96MHZ/160MHZ 0.45UM 3.3V/5V 44PLCC - Rail/Tube |

| A40MX04-1PL44MX3 | 制造商:Microsemi Corporation 功能描述:FPGA 6K GATES 547 CELLS 96MHZ/160MHZ 0.45UM 3.3V/5V 44PLCC - Rail/Tube |

| A40MX04-1PL68 | 功能描述:IC FPGA MX SGL CHIP 6K 68-PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 標準包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計:36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

| A40MX04-1PL68I | 功能描述:IC FPGA MX SGL CHIP 6K 68-PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:MX 標準包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計:36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

| A40MX04-1PL68M | 制造商:Microsemi Corporation 功能描述:FPGA 6K GATES 547 CELLS 96MHZ/160MHZ 0.45UM 3.3V/5V 68PLCC - Rail/Tube 制造商:Microsemi Corporation 功能描述:IC FPGA MX SGL CHIP 6K 68-PLCC 制造商:Microsemi Corporation 功能描述:IC FPGA 57 I/O 68PLCC |

發(fā)布緊急采購,3分鐘左右您將得到回復。