- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4481 > A3P600-FG256I (Microsemi SoC)IC FPGA 1KB FLASH 600K 256-FBGA PDF資料下載

參數(shù)資料

| 型號: | A3P600-FG256I |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 219/220頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1KB FLASH 600K 256-FBGA |

| 標準包裝: | 90 |

| 系列: | ProASIC3 |

| RAM 位總計: | 110592 |

| 輸入/輸出數(shù): | 177 |

| 門數(shù): | 600000 |

| 電源電壓: | 1.425 V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FPBGA(17x17) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁當前第219頁第220頁

ProASIC3 DC and Switching Characteristics

2-84

Revision 13

Global Resource Characteristics

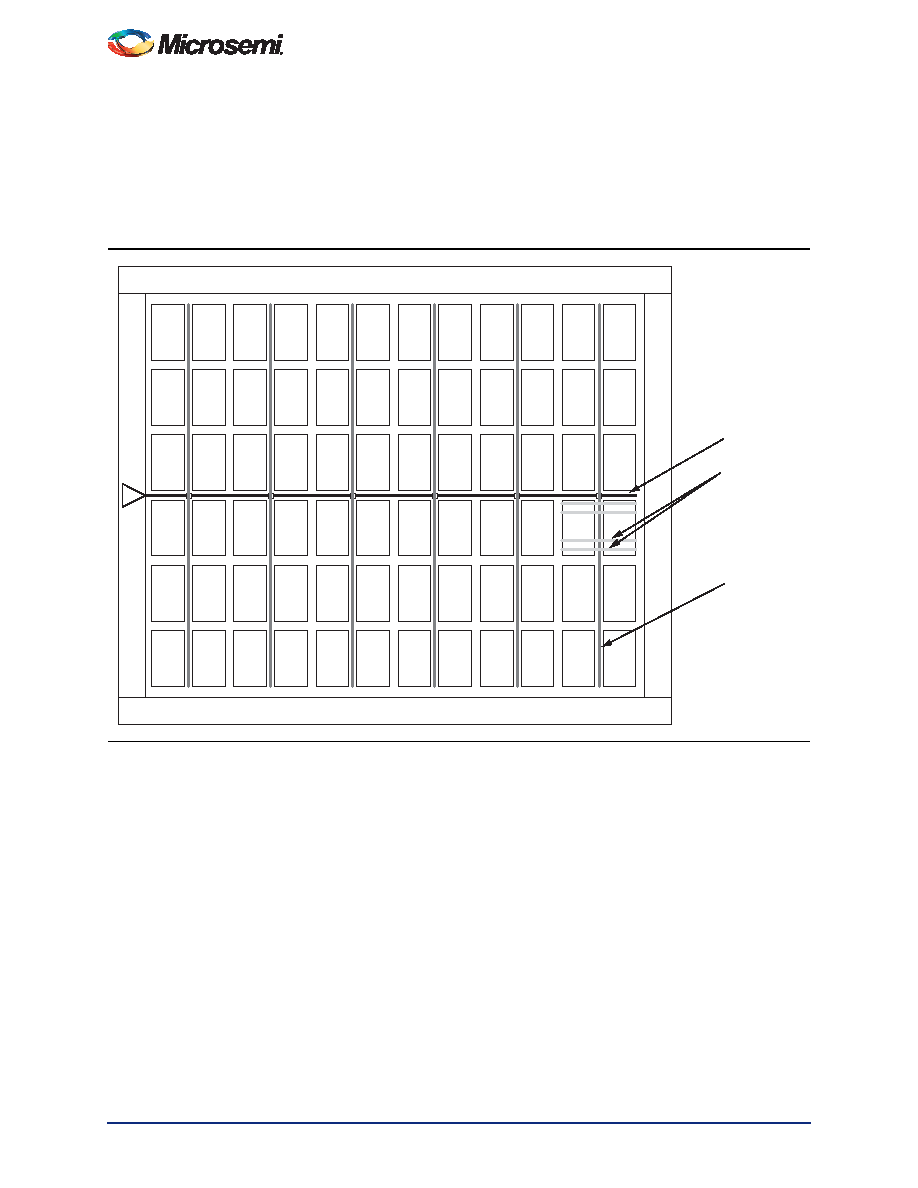

A3P250 Clock Tree Topology

Clock delays are device-specific. Figure 2-27 is an example of a global tree used for clock routing. The

global tree presented in Figure 2-27 is driven by a CCC located on the west side of the A3P250 device. It

is used to drive all D-flip-flops in the device.

Global Tree Timing Characteristics

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not

include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven

and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer

present minimum and maximum global clock delays within each device. Minimum and maximum delays

are measured with minimum and maximum loading.

Figure 2-27 Example of Global Tree Use in an A3P250 Device for Clock Routing

Central

Global Rib

VersaTile

Rows

Global Spine

CCC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A3P600-FGG256I | IC FPGA 1KB FLASH 600K 256-FBGA |

| M1A3P600-FG256I | IC FPGA 1KB FLASH 600K 256-FBGA |

| GBB100DHBN | CONN EDGECARD 200PS R/A .050 SLD |

| GBB100DHBD | CONN EDGECARD 200PS R/A .050 SLD |

| RSA49DTKI-S288 | CONN EDGECARD 98POS .125 EXTEND |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A3P600-FG484 | 功能描述:IC FPGA 1KB FLASH 600K 484-FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 標準包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計:36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應(yīng)商設(shè)備封裝:256-FPBGA(17x17) |

| A3P600-FG484I | 功能描述:IC FPGA 1KB FLASH 600K 484-FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 標準包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A3P600-FGG144 | 功能描述:IC FPGA 235I/O 144FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 標準包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計:221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| A3P600-FGG144ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P600-FGG144I | 功能描述:IC FPGA 1KB FLASH 600K 144-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 標準包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計:36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應(yīng)商設(shè)備封裝:256-FPBGA(17x17) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。