- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄209983 > A3P030-FVQG100 FPGA, 768 CLBS, 30000 GATES, 350 MHz, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | A3P030-FVQG100 |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 768 CLBS, 30000 GATES, 350 MHz, PQFP100 |

| 封裝: | 14 X 14 MM, 1 MM HEIGHT, 0.50 MM PITCH, GREEN, VQFP-100 |

| 文件頁數(shù): | 49/49頁 |

| 文件大小: | 5893K |

| 代理商: | A3P030-FVQG100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁

ProASIC3 DC and Switching Characteristics

2- 82

v1.3

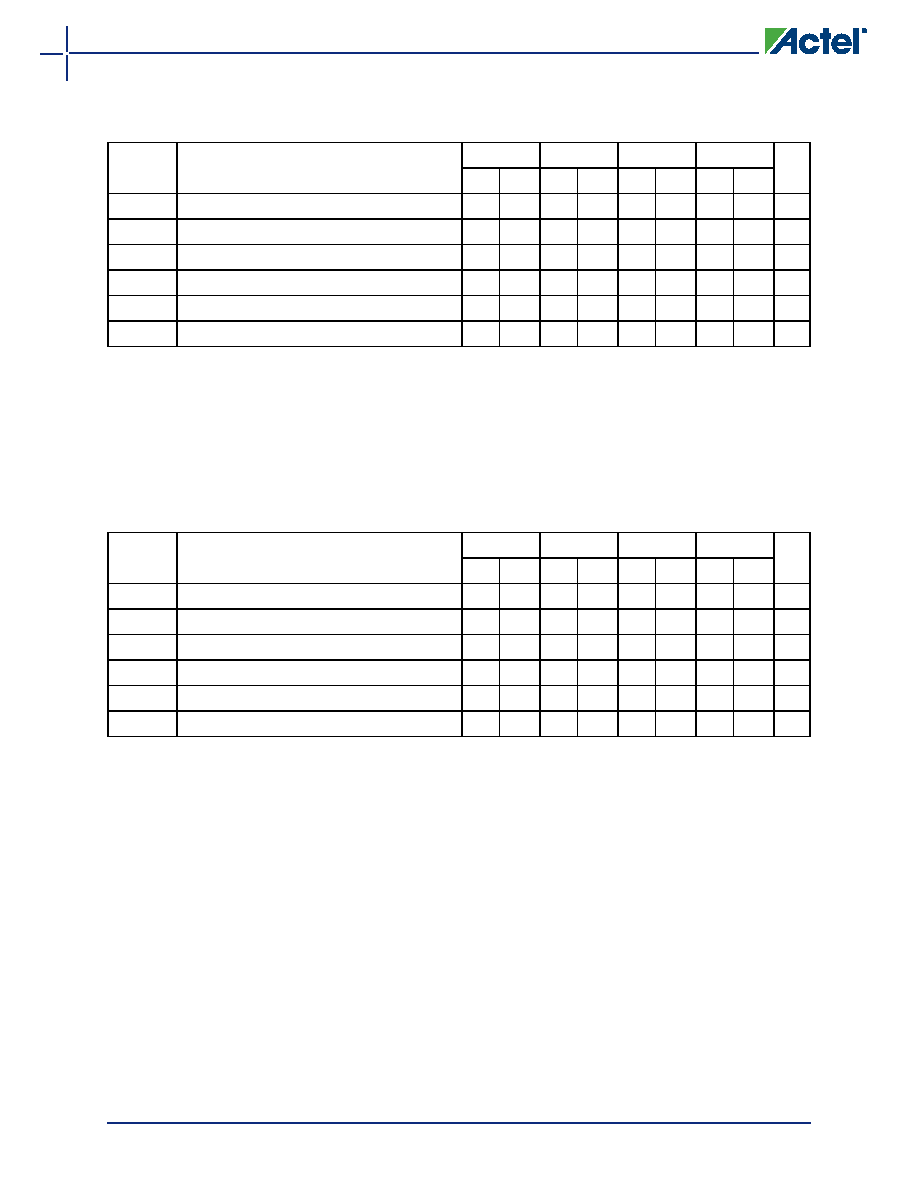

Table 2-104 A3P600 Global Resource

Commercial-Case Conditions: TJ = 70°C, VCC = 1.425 V

Parameter

Description

–2

–1

Std.

–F

Units

Min.1 Max.2 Min.1 Max.2 Min.1 Max.2 Min.1 Max.2

tRCKL

Input LOW Delay for Global Clock

0.87 1.09 0.99 1.24 1.17 1.46 1.40 1.75

ns

tRCKH

Input HIGH Delay for Global Clock

0.861.11 0.981.271.151.491.381.79

ns

tRCKMPWH Minimum Pulse Width HIGH for Global Clock

ns

tRCKMPWL Minimum Pulse Width LOW for Global Clock

ns

tRCKSW

Maximum Skew for Global Clock

0.26

0.29

0.34

0.41

ns

FRMAX

Maximum Frequency for Global Clock

MHz

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential

element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element,

located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.

Table 2-105 A3P1000 Global Resource

Commercial-Case Conditions: TJ = 70°C, VCC = 1.425 V

Parameter

Description

–2

–1

Std.

–F

Units

Min.1 Max.2 Min.1 Max.2 Min.1 Max.2 Min.1 Max.2

tRCKL

Input LOW Delay for Global Clock

0.94 1.16 1.07 1.32 1.26 1.55 1.51 1.86

ns

tRCKH

Input HIGH Delay for Global Clock

0.931.19 1.061.351.241.591.491.91

ns

tRCKMPWH Minimum Pulse Width HIGH for Global Clock

ns

tRCKMPWL Minimum Pulse Width LOW for Global Clock

ns

tRCKSW

Maximum Skew for Global Clock

0.26

0.29

0.35

0.41

ns

FRMAX

Maximum Frequency for Global Clock

MHz

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential

element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element,

located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A3P125-FFGG144 | FPGA, 3072 CLBS, 125000 GATES, 350 MHz, PBGA144 |

| A3P125-FPQG208 | FPGA, 3072 CLBS, 125000 GATES, 350 MHz, PQFP208 |

| A3P125-FTQG144 | FPGA, 3072 CLBS, 125000 GATES, 350 MHz, PQFP144 |

| A3P125-FVQG100 | FPGA, 3072 CLBS, 125000 GATES, 350 MHz, PQFP100 |

| A42MX36-1BGG304 | FPGA, 2438 CLBS, 36000 GATES, PBGA304 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A3P030-FVQG144 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P030-FVQG144ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P030-FVQG144I | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P030-FVQG144PP | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| A3P030-PQ144 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。