- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4365 > A1240A-PG132C (Microsemi SoC)IC FPGA 4K GATES 132-CPGA COM PDF資料下載

參數(shù)資料

| 型號: | A1240A-PG132C |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 5/54頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 4K GATES 132-CPGA COM |

| 標(biāo)準(zhǔn)包裝: | 21 |

| 系列: | ACT™ 2 |

| LAB/CLB數(shù): | 684 |

| 輸入/輸出數(shù): | 104 |

| 門數(shù): | 4000 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類型: | 通孔 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 132-BCPGA |

| 供應(yīng)商設(shè)備封裝: | 132-CPGA(34.54x34.54) |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

ACT 2 Family FPGAs

R e visio n 8

2 -7

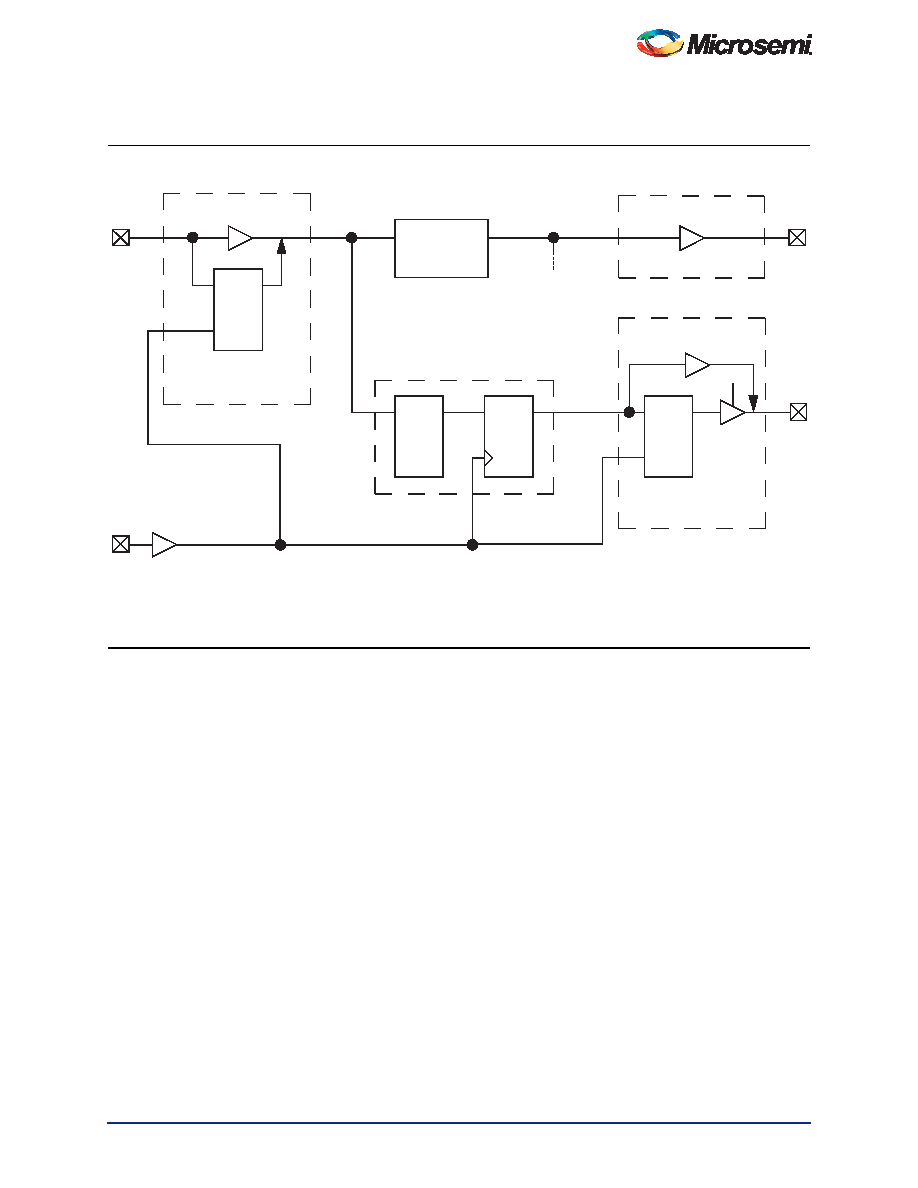

ACT 2 Timing Model1

Notes:

1. Values shown for A1240A-2 at worst-case commercial conditions.

2. Input module predicted routing delay

Figure 2-1

Timing Model

Output Delays

Internal Delays

Input Delays

tINH = 2.0 ns

tINSU= 4.0 ns

I/O Module

D

Q

tINGL= 4.7 ns

tINYL= 2.6 ns tIRD2= 4.8 ns(2)

Combinatorial

Logic Module

tPD= 3.8 ns

Sequential

Logic Module

I/O Module

tRD1 = 1.4 ns

tDLH = 8.0 ns

I/O Module

ARRAY

CLOCKS

FMAX= 100 MHz

Combin-

atorial

Logic

Included

in t

SUD

D

Q

D

Q

tOUTH = 0.0 ns

tOUTSU= 0.4 ns

tGLH = 9.0 ns

tDLH = 8.0 ns

tENHZ = 7.1 ns

tRD1= 1.4 ns

tCO= 3.8 ns

tSUD= 0.4 ns

tHD= 0.0 ns

tRD4 = 3.1 ns

tRD8 = 4.7 ns

Predicted

Routing

Delays

tCKH= 11.8 ns

G

FO = 256

tRD2 = 1.7 ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP20K300EFC672-2N | IC APEX 20KE FPGA 300K 672-FBGA |

| EP20K300EFC672-2 | IC APEX 20KE FPGA 300K 672-FBGA |

| APA750-FGG676 | IC FPGA PROASIC+ 750K 676-FBGA |

| APA750-FG676 | IC FPGA PROASIC+ 750K 676-FBGA |

| EP4CE115F29I8L | IC CYCLONE IV FPGA 115K 780-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A1240A-PG132M | 制造商:Microsemi Corporation 功能描述:FPGA ACT 2 Family 4K Gates 684 Cells 90MHz 1.0um Technology 5V 132-Pin CPGA |

| A1240A-PG160B | 制造商:MICROSEMI 制造商全稱:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1240A-PG160C | 制造商:MICROSEMI 制造商全稱:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1240A-PG160I | 制造商:MICROSEMI 制造商全稱:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1240A-PG160M | 制造商:MICROSEMI 制造商全稱:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。