- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25569 > 9LPR501SGLF (INTEGRATED DEVICE TECHNOLOGY INC) SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 PDF資料下載

參數(shù)資料

| 型號(hào): | 9LPR501SGLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-64 |

| 文件頁(yè)數(shù): | 12/21頁(yè) |

| 文件大小: | 197K |

| 代理商: | 9LPR501SGLF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

IDTTM/ICSTM

64-pin CK505 w/Fully Integrated Voltage Regulator

1118N—05/19/11

Advance Information

ICS9LPR501

64-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR

2

Datasheet

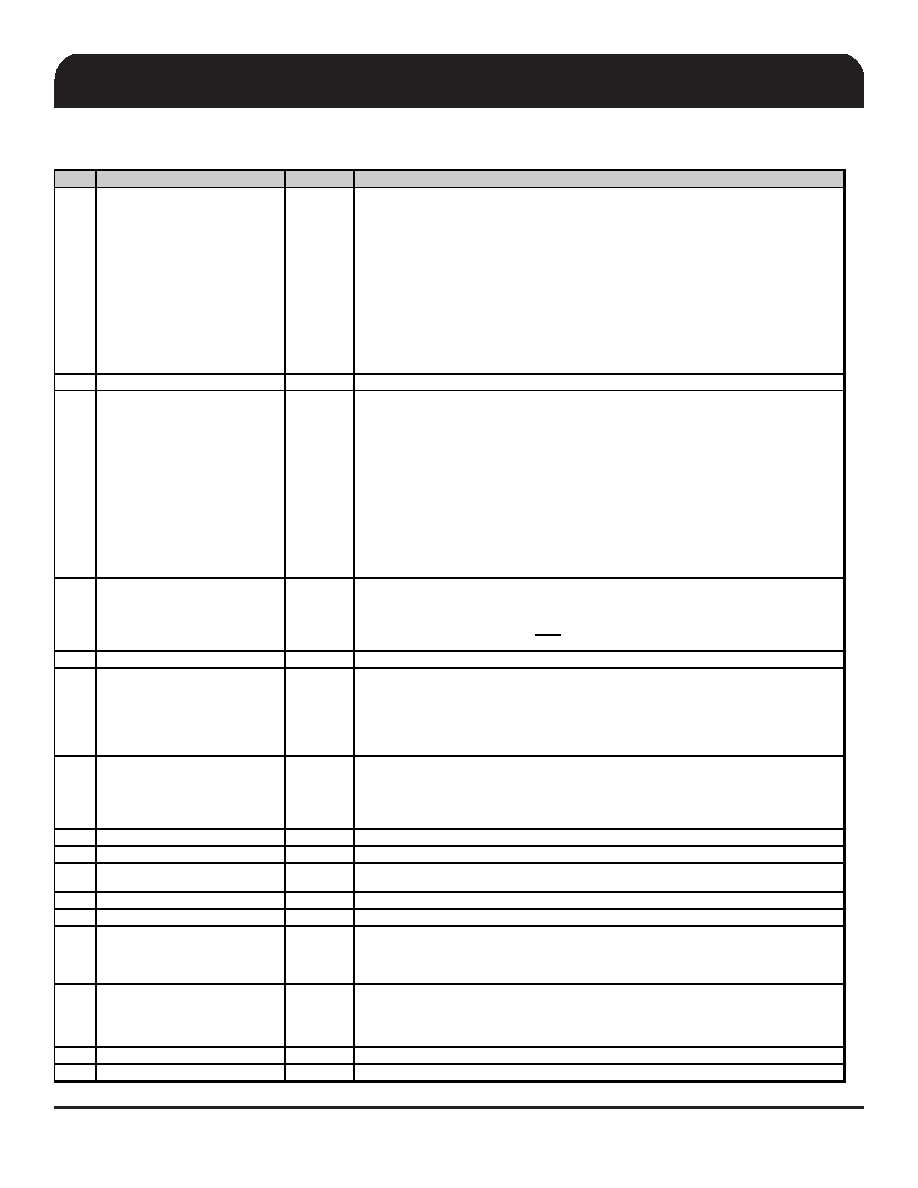

PIN #

PIN NAME

TYPE

DESCRIPTION

1

PCI0/CR#_A

I/O

3.3V PCI clock output or Clock Request control A for either SRC0 or SRC2 pair

The power-up default is PCI0 output, but this pin may also be used as a Clock Request control

of SRC pair 0 or SRC pair 2 via SMBus. Before configuring this pin as a Clock Request Pin, the

PCI output must first be disabled in byte 2, bit 0 of SMBus address space . After the PCI output

is disabled (high-Z), the pin can then be set to serve as a Clock Request pin for either SRC pair

2 or pair 0 using the CR#_A_EN bit located in byte 5 of SMBUs address space.

Byte 5, bit 7

0 = PCI0 enabled (default)

1= CR#_A enabled. Byte 5, bit 6 controls whether CR#_A controls SRC0 or SRC2 pair

Byte 5, bit 6

0 = CR#_A controls SRC0 pair (default),

1= CR#_A controls SRC2 pair

2

VDDPCI

PWR

Power supply pin for the PCI outputs, 3.3V nominal

3

PCI1/CR#_B

I/O

3.3V PCI clock output/Clock Request control B for either SRC1 or SRC4 pair

The power-up default is PCI1 output, but this pin may also be used as a Clock Request control

of SRC pair 1 or SRC pair 4 via SMBus. Before configuring this pin as a Clock Request Pin, the

PCI output must first be disabled in byte 2, bit 1 of SMBus address space . After the PCI output

is disabled (high-Z), the pin can then be set to serve as a Clock Request pin for either SRC pair

1 or pair 4 using the CR#_B_EN bit located in byte 5 of SMBUs address space.

Byte 5, bit 5

0 = PCI1 enabled (default)

1= CR#_B enabled. Byte 5, bit 6 controls whether CR#_B controls SRC1 or SRC4 pair

Byte 5, bit 4

0 = CR#_B controls SRC1 pair (default)

1= CR#_B controls SRC4 pair

4PCI2/TME

I/O

3.3V PCI clock output / Trusted Mode Enable (TME) Latched Input. This pin is sampled on

power-up as follows

0 = Overclocking of CPU and SRC Allowed

1 = Overclocking of CPU and SRC NOT allowed

After being sampled on power-up, this pin becomes a 3.3V PCI Output

5

PCI3

OUT

3.3V PCI clock output.

6

PCI4/SRC5_EN

I/O

3.3V PCI clock output / SRC5 pair or PCI_STOP#/CPU_STOP# enable strap. On powerup, the

logic value on this pin determines if the SRC5 pair is enabled or if CPU_STOP#/PCI_STOP# is

enabled (pins 37 and 38). The latched value controls the pin function on pins 37 and 38 as

follows

0 = PCI_STOP#/CPU_STOP#

1 = SRC5/SRC5#

7

PCI_F5/ITP_EN

I/O

Free running PCI clock output and ITP/SRC8 enable strap. This output is not affected by the

state of the PCI_STOP# pin. On powerup, the state of this pin determines whether pins 38 and

39 are an ITP or SRC pair.

0 =SRC8/SRC8#

1 = ITP/ITP#

8

GNDPCI

PWR

Ground for PCI clocks.

9

VDD48

PWR

Power supply for USB clock, nominal 3.3V.

10

USB_48MHz/FSLA

I/O

Fixed 48MHz USB clock output. 3.3V./ 3.3V tolerant input for CPU frequency selection. Refer to

input electrical characteristics for Vil_FS and Vih_FS values.

11

GND48

PWR

Ground pin for the 48MHz outputs.

12

VDD96_IO

PWR

Power supply for DOT96 outputs, VDD96_IO is 1.05 to 3.3V with +/-5% tolerance

13

DOTT_96/SRCT0

OUT

True clock of SRC or DOT96. The power-up default function is SRC0. After powerup, this pin

function may be changed to DOT96 via SMBus Byte 1, bit 7 as follows:

0= SRC0

1=DOT96

14

DOTC_96/SRCC0

OUT

Complement clock of SRC or DOT96. The power-up default function is SRC0#. After powerup,

this pin function may be changed to DOT96# via SMBus Byte 1, bit 7 as follows

0= SRC0#

1=DOT96#

15

GND

PWR

Ground pin for the DOT96 clocks.

16

VDD

PWR

Power supply for SRC / SE1 and SE2 clocks, 3.3V nominal.

Pin Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9LPR501SGLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 |

| 9LPR501YGT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 |

| 9LPR502YGLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 |

| 9LPRS365BKLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC64 |

| 9LPRS365BGLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9LPR501SGLFT | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 PC MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9LPR501YGLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:64-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR |

| 9LPR502HGLF | 制造商:Integrated Device Technology Inc 功能描述:PC CLOCK, TSSOP56 - Rail/Tube |

| 9LPR502HGLFT | 制造商:Integrated Device Technology Inc 功能描述:PC CLOCK, TSSOP56 - Rail/Tube |

| 9LPR502SGLF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 PC MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。