- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25565 > 9ERS3165BGILFT (INTEGRATED DEVICE TECHNOLOGY INC) 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 PDF資料下載

參數(shù)資料

| 型號: | 9ERS3165BGILFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, TSSOP-64 |

| 文件頁數(shù): | 21/26頁 |

| 文件大小: | 319K |

| 代理商: | 9ERS3165BGILFT |

IDTTM

Embedded 64-Pin Industrial Temperature Range CK505 Compatible Clock

1613B—01/25/10

ICS9ERS3165

Embedded 64-Pin Industrial Temperature Range CK505 Compatible Clock

4

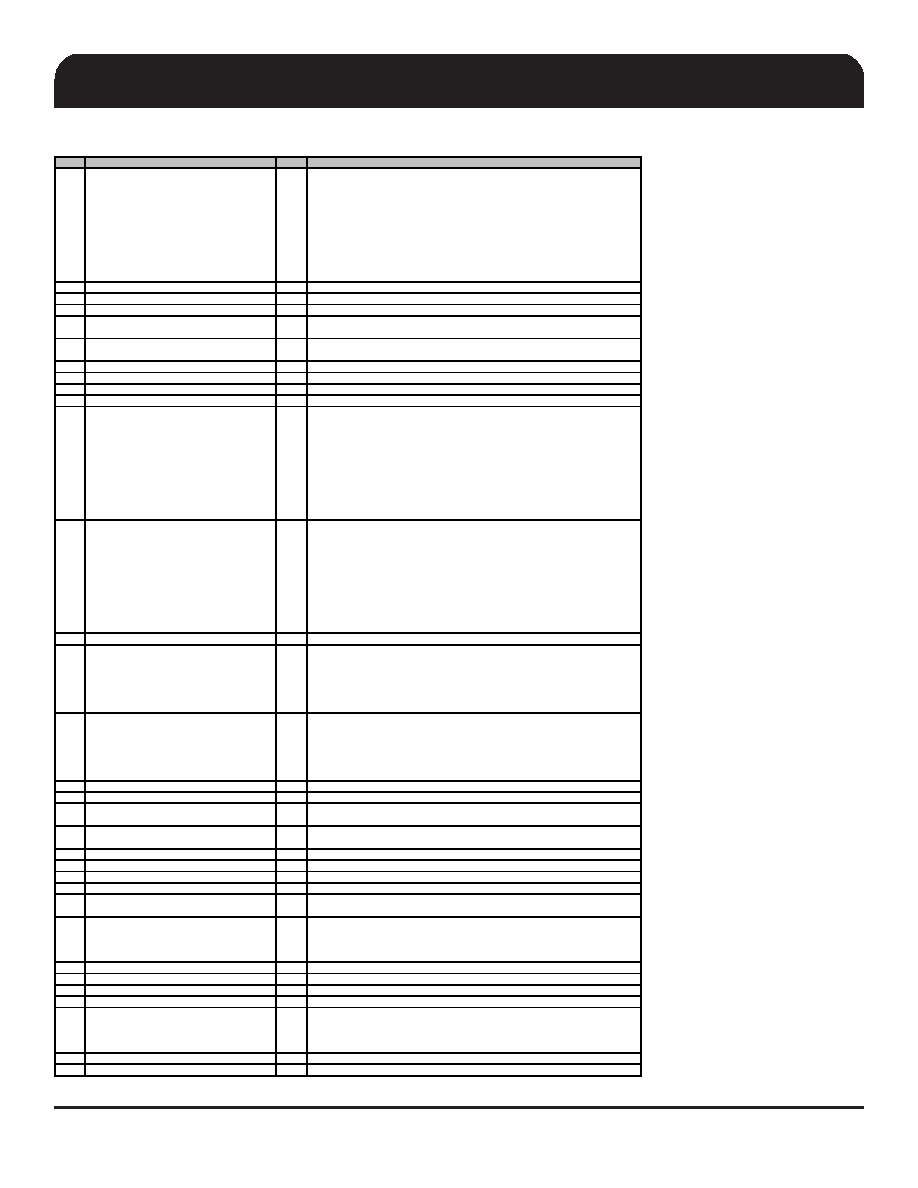

TSSOP Pin Description (Continued)

PIN #

PIN NAME

TYPE

DESCRIPTION

33

SRCT_LR11/CR#_H

I/O

SRC11 true or Clock Request control H for SRC10 pair

The power-up default is SRC11, but this pin may also be used as a Clock Request

control of SRC10 via SMBus. Before configuring this pin as a Clock Request Pin, the

SRC11 output pair must first be disabled in byte 3, bit 7 of SMBus configuration

space After the SRC11 output is disabled (high-Z), the pin can then be set to serve

as a Clock Request for SRC10 pair using byte 6, bit 4 of SMBus configuration space

Byte 6, bit 4

0 = SRC11 enabled (default)

1= CR#_H controls SRC10.

34

SRCT_LR10

OUT True clock of differential SRC clock pair.

35

SRCC_LR10

OUT Complement clock of differential SRC clock pair.

36

VDDSRCI/O

PWR

1.05V to 3.3V from external power supply

37

CPU_STOP#

IN

Stops all CPU Clocks, except those set to be free running clocks. In AMT mode 3

bits are shifted in from the ICH to set the FSC, FSB, FSA values

38

PCI_STOP#

IN

Stops all PCI Clocks, except those set to be free running clocks. In AMT mode 3 bits

are shifted in from the ICH to set the FSC, FSB, FSA values

39

VDDSRC

PWR VDD pin for SRC Pre-drivers, 3.3V nominal

40

SRCC_LR6

OUT Complement clock of low power differential SRC clock pair.

41

SRCT_LR6

OUT True clock of low power differential SRC clock pair.

42

GNDSRC

PWR Ground for SRC clocks

43

SRCC_LR7/CR#_E

I/O

SRC7 complement or Clock Request control E for SRC6 pair

The power-up default is SRC7#, but this pin may also be used as a Clock Request

control of SRC6 via SMBus. Before configuring this pin as a Clock Request Pin, the

SRC7 output pair must first be disabled in byte 3, bit 3 of SMBus configuration space

. After the SRC output is disabled (high-Z), the pin can then be set to serve as a

Clock Request for SRC6 pair using byte 6, bit 7 of SMBus configuration space

Byte 6, bit 7

0 = SRC7# enabled (default)

1= CR#_E controls SRC6.

44

SRCT_LR7/CR#_F

I/O

SRC7 true or Clock Request control 8 for SRC8 pair

The power-up default is SRC7, but this pin may also be used as a Clock Request

control of SRC8 via SMBus. Before configuring this pin as a Clock Request Pin, the

SRC7 output pair must first be disabled in byte 3, bit 3 of SMBus configuration space

After the SRC output is disabled (high-Z), the pin can then be set to serve as a Clock

Request for SRC8 pair using byte 6, bit 6 of SMBus configuration space

Byte 6, bit 6

0 = SRC7# enabled (default)

1 = CR#_F controls SRC8.

45

VDDSRCI/O

PWR

1.05V to 3.3V from external power supply

46

CPUC_ITP_LR2/SRCC8

OUT

Complement clock of low power differential CPU2/Complement clock of differential

SRC pair. The function of this pin is determined by the latched input value on pin 7,

PCIF5/ITP_EN on powerup. The function is as follows:

Pin 7 latched input Value

0 = SRC8#

1 = ITP#

47

CPUT_ITP_LR2/SRCT8

OUT

True clock of low power differential CPU2/True clock of differential SRC pair. The

function of this pin is determined by the latched input value on pin 7, PCIF5/ITP_EN

on powerup. The function is as follows:

Pin 7 latched input Value

0 = SRC8

1 = ITP

48

NC

N/A

No Connect

49

VDDCPU_IO

PWR

1.05V to 3.3V from external power supply

50

CPUC_F_LR1

OUT

Complement clock of low power differenatial CPU clock pair. This clock will be free-

running during iAMT.

51

CPUT_F_LR1

OUT

True clock of low power differential CPU clock pair. This clock will be free-running

during iAMT.

52

GNDCPU

PWR Ground Pin for CPU Outputs

53

CPUC_LR0

OUT Complement clock of low power differential CPU clock pair.

54

CPUT_LR0

OUT True clock of low power differential CPU clock pair.

55

VDDCPU

PWR Power Supply 3.3V nominal.

56

CK_PWRGD/PD#

IN

Notifies CK505 to sample latched inputs, or iAMT entry/exit, or PWRDWN# mode

57

FSLB/TEST_MODE

IN

3.3V tolerant input for CPU frequency selection. Refer to input electrical

characteristics for Vil_FS and Vih_FS values. TEST_MODE is a real time input to

select between Hi-Z and REF/N divider mode while in test mode. Refer to Test

Clarification Table.

58

GNDREF

PWR Ground pin for crystal oscillator circuit

59

X2

OUT Crystal output, nominally 14.318MHz.

60

X1

IN

Crystal input, Nominally 14.318MHz.

61

VDDREF

PWR Power pin for the REF outputs, 3.3V nominal.

62

REF/FSLC/TEST_SEL

I/O

3.3V 14.318MHz reference clock/3.3V tolerant low threshold input for CPU frequency

selection. Refer to input electrical characteristics for Vil_FS and Vih_FS values/

TEST_SEL: 3-level latched input to enable test mode. Refer to Test Clarification

Table.

63

SDATA

I/O

Data pin for SMBus circuitry, 5V tolerant.

64

SCLK

IN

Clock pin of SMBus circuitry, 5V tolerant.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9EX21501AKLFT | 21501 SERIES, PLL BASED CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC64 |

| 9EX21501AKLF | 21501 SERIES, PLL BASED CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC64 |

| 9EX21501AKILF | 21501 SERIES, PLL BASED CLOCK DRIVER, 15 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC64 |

| 9EX21801AKLF | PLL BASED CLOCK DRIVER, PQCC72 |

| 9EX21801AKLFT | PLL BASED CLOCK DRIVER, PQCC72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9ERS3165BGLF | 功能描述:時鐘合成器/抖動清除器 EMBEDDED CK505 COMPATIBLE CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9ERS3165BGLFT | 功能描述:時鐘合成器/抖動清除器 EMBEDDED CK505 COMPATIBLE CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9ERS3165BKILF | 功能描述:時鐘合成器/抖動清除器 EMBEDDED CK505 COMPATIBLE CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9ERS3165BKILFT | 功能描述:時鐘合成器/抖動清除器 EMBEDDED CK505 COMPATIBLE CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9ERS3165BKLF | 功能描述:時鐘合成器/抖動清除器 EMBEDDED CK505 COMPATIBLE CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。