- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25565 > 9DB833AGLFT (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF資料下載

參數(shù)資料

| 型號: | 9DB833AGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封裝: | ROHS COMPLIANT, TSSOP-48 |

| 文件頁數(shù): | 12/18頁 |

| 文件大?。?/td> | 226K |

| 代理商: | 9DB833AGLFT |

9DB833

EIGHT OUTPUT DIFFERENTIAL BUFFER FOR PCIE GEN3

IDT

EIGHT OUTPUT DIFFERENTIAL BUFFER FOR PCIE GEN3

3

9DB833

REV C 052411

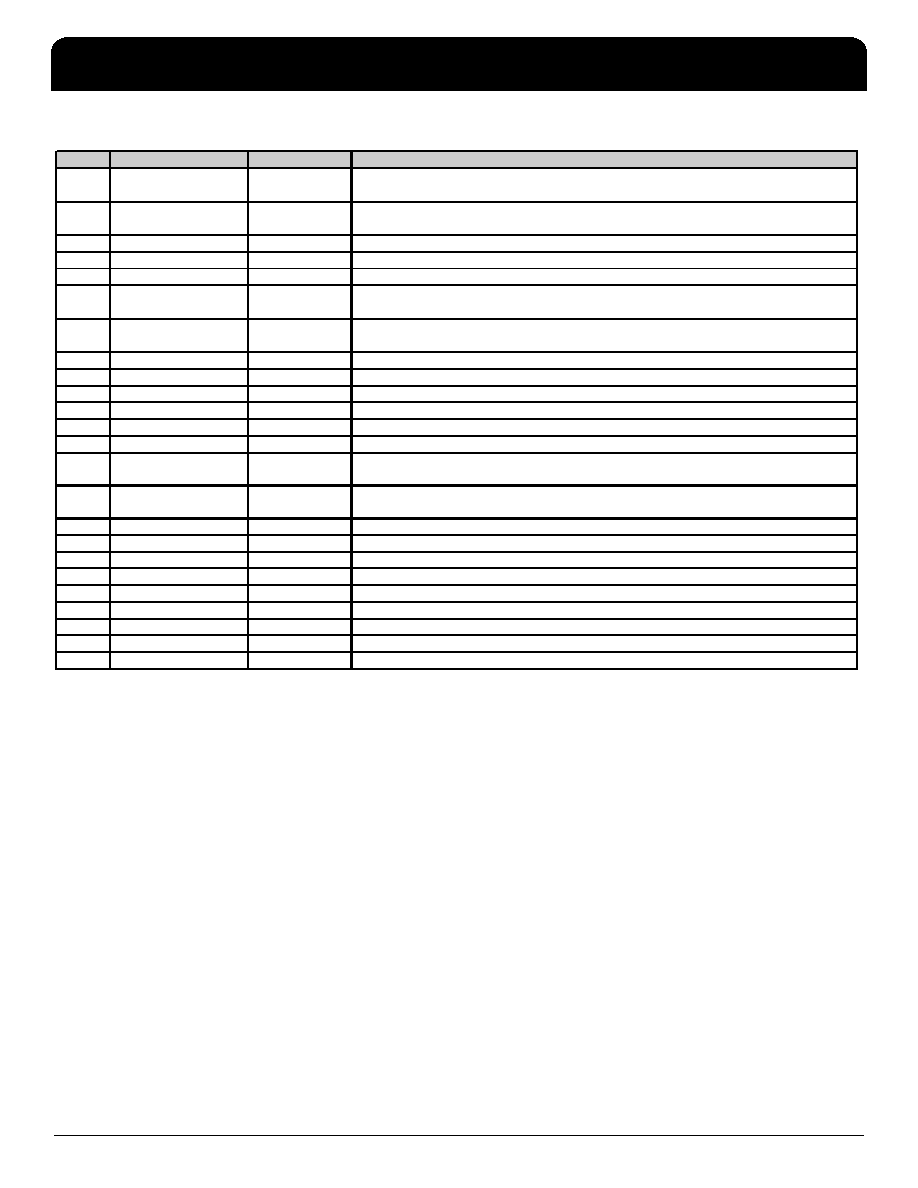

Pin Descriptions

PIN #

PIN NAME

PIN TYPE

DESCR IPTION

1SRC_DIV#

IN

Active low Input for determining SRC output frequency SRC or SRC/2.

0 = SRC/2, 1= SRC

2VDDR

PWR

3.3V power for differential input clock (receiver). This VDD should be treated as an

analog power rail and filtered appropriately.

3

GND

PWR

Ground pin.

4

SRC_IN

IN

0.7 V D ifferential SR C TRUE input

5

SRC_IN#

IN

0.7 V D ifferential SR C COMPLEMENTAR Y input

6OE0#

IN

Active low input for enabling DIF pair 0.

1 =disable outputs, 0 = enable outputs

7OE3#

IN

Active low input for enabling DIF pair 3.

1 =disable outputs, 0 = enable outputs

8

DIF_0

OUT

0.7V differential true clock output

9

DIF_0#

OUT

0.7V differential Complementary clock output

10

GND

PWR

Ground pin.

11

VDD

PWR

Power supply, nominal 3.3V

12

DIF_1

OUT

0.7V differential true clock output

13

DIF_1#

OUT

0.7V differential Complementary clock output

14

OE1#

IN

Active low input for enabling DIF pair 1.

1 =disable outputs, 0 = enable outputs

15

OE2#

IN

Active low input for enabling DIF pair 2.

1 =disable outputs, 0 = enable outputs

16

DIF_2

OUT

0.7V differential true clock output

17

DIF_2#

OUT

0.7V differential Complementary clock output

18

GND

PWR

Ground pin.

19

VDD

PWR

Power supply, nominal 3.3V

20

DIF_3

OUT

0.7V differential true clock output

21

DIF_3#

OUT

0.7V differential Complementary clock output

22

BYP#_HIBW_LOBW

IN

Tri-level input to select bypass mode, Hi BW PLL, or Lo BW PLL mode

23

SMBC LK

IN

Clock pin of SMBUS circuitry, 5V tolerant

24

SMBD AT

I/O

Data pin of SMBUS circuitry, 5V tolerant

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9DB833AGILFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB833AFILFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB833AFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB833AFLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DBL411AGLFT | LOW SKEW CLOCK DRIVER, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9DBL0242BKILF | 功能描述:IC CLK FANOUT/BUFF ZD 24VFQFPN 制造商:idt, integrated device technology inc 系列:- 包裝:托盤 零件狀態(tài):在售 PLL:是 主要用途:PCI Express(PCIe) 輸入:HCSL 輸出:HCSL 電路數(shù):1 比率 - 輸入:輸出:1:2 差分 - 輸入:輸出:是/是 頻率 - 最大值:200MHz 電壓 - 電源:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:24-VFQFN 裸露焊盤 供應(yīng)商器件封裝:24-VFQFPN(4x4) 標(biāo)準(zhǔn)包裝:490 |

| 9DBL0252BKILF | 功能描述:CLOCK BUFFER 3.3V LP-HCSL PCIE 制造商:idt, integrated device technology inc 系列:* 包裝:托盤 零件狀態(tài):在售 PLL:是 主要用途:PCI Express(PCIe) 輸入:HCSL 輸出:HCSL 電路數(shù):1 比率 - 輸入:輸出:1:2 差分 - 輸入:輸出:是/是 頻率 - 最大值:200MHz 電壓 - 電源:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:24-VFQFN 裸露焊盤 供應(yīng)商器件封裝:24-VFQFPN(4x4) 標(biāo)準(zhǔn)包裝:490 |

| 9DBL0442BKILF | 功能描述:IC CLK FANOUT/BUFF ZD 32VFQFPN 制造商:idt, integrated device technology inc 系列:- 包裝:托盤 零件狀態(tài):在售 PLL:是 主要用途:PCI Express(PCIe) 輸入:HCSL 輸出:HCSL 電路數(shù):1 比率 - 輸入:輸出:1:4 差分 - 輸入:輸出:是/是 頻率 - 最大值:200MHz 電壓 - 電源:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:32-VFQFN 裸露焊盤 供應(yīng)商器件封裝:32-VFQFPN(5x5) 標(biāo)準(zhǔn)包裝:490 |

| 9DBL0452BKILF | 功能描述:IC CLK BUFFER ZD 32-VFQFPN 制造商:idt, integrated device technology inc 系列:* 包裝:托盤 零件狀態(tài):在售 PLL:是 主要用途:PCI Express(PCIe) 輸入:HCSL 輸出:HCSL 電路數(shù):1 比率 - 輸入:輸出:1:4 差分 - 輸入:輸出:是/是 頻率 - 最大值:200MHz 電壓 - 電源:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:32-VFQFN 裸露焊盤 供應(yīng)商器件封裝:32-VFQFPN(5x5) 標(biāo)準(zhǔn)包裝:490 |

| 9DBL0452BKILFT | 功能描述:IC CLK BUFFER ZD 32-VFQFPN 制造商:idt, integrated device technology inc 系列:- 零件狀態(tài):在售 PLL:是 主要用途:PCI Express(PCIe) 輸入:HCSL 輸出:HCSL 電路數(shù):1 比率 - 輸入:輸出:1:4 差分 - 輸入:輸出:是/是 頻率 - 最大值:200MHz 電壓 - 電源:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:32-VFQFN 裸露焊盤 供應(yīng)商器件封裝:32-VFQFPN(5x5) 標(biāo)準(zhǔn)包裝:2,500 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。