- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25565 > 9DB833AFLF (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF資料下載

參數(shù)資料

| 型號(hào): | 9DB833AFLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封裝: | ROHS COMPLIANT, SSOP-48 |

| 文件頁數(shù): | 15/18頁 |

| 文件大?。?/td> | 226K |

| 代理商: | 9DB833AFLF |

9DB833

EIGHT OUTPUT DIFFERENTIAL BUFFER FOR PCIE GEN3

IDT

EIGHT OUTPUT DIFFERENTIAL BUFFER FOR PCIE GEN3

6

9DB833

REV C 052411

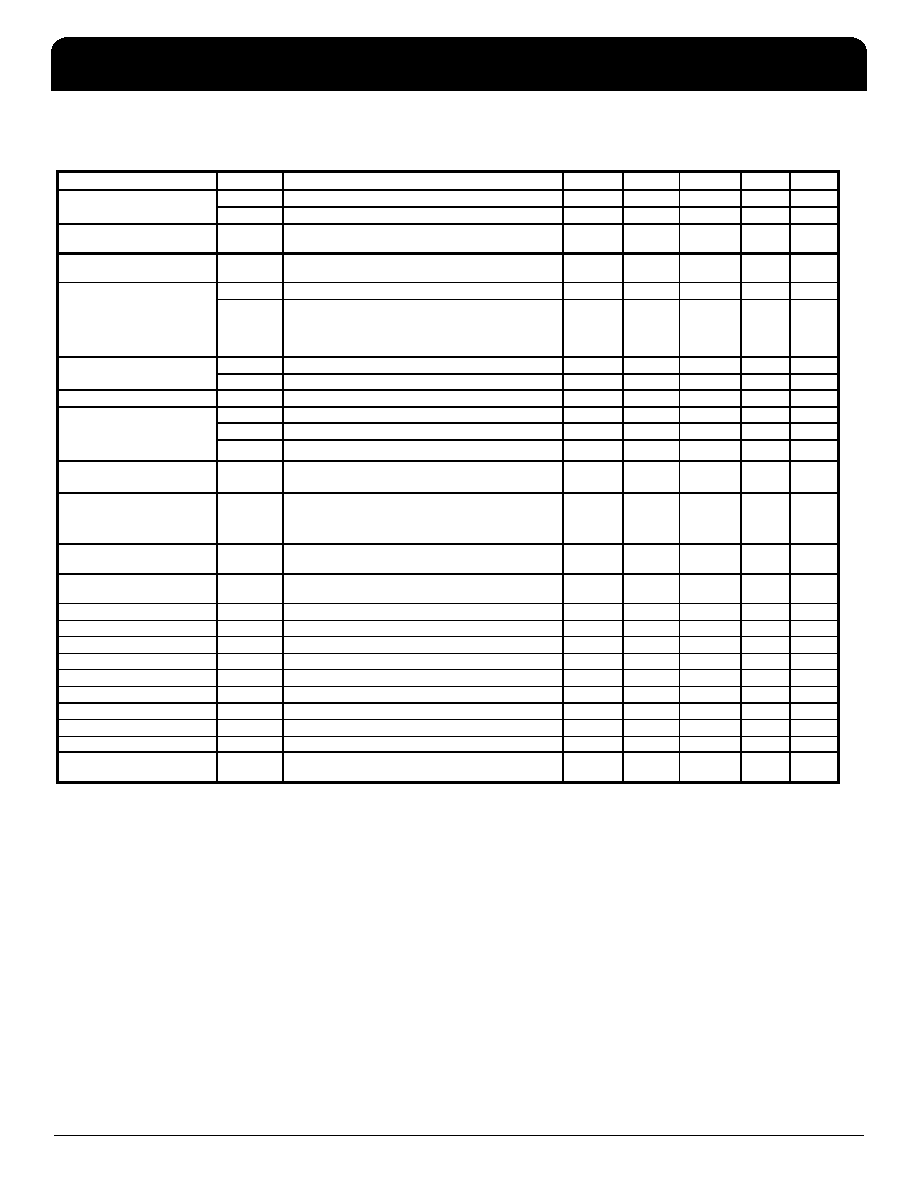

Electrical Characteristics–Input/Supply/Common Output Parameters

TA = TCOM or TIND; Supply Voltage VDD = 3.3 V +/-5%

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS N OTES

T

COM

C ommmercial range

0

70

°C

1

TIND

Industrial range

-40

85

°C

1

Input High Voltage

V

IH

Single-ended inputs, except SMBus, low threshold

and tri-level inputs

2

V

DD + 0.3

V1

Input Low Voltage

V

IL

Single-ended inputs, except SMBus, low threshold

and tri-level inputs

GND - 0.3

0.8

V

1

IIN

Single-ended inputs, VIN = GND, VIN = VDD

-5

5

uA

1

IINP

Single-ended inputs

V

IN = 0 V; I nputs with interna l pu ll-u p resistors

VIN = VDD; Inputs with internal pull-down resistors

-200

200

uA

1

Fibyp

VDD = 3.3 V, Bypass mode

5

166

MHz

2

F

ip ll

V

DD = 3.3 V, 10 0MHz P LL m ode

50

100.00

110

MHz

2

Pin Inductance

Lpin

7nH

1

C

IN

Logic Inputs, except DIF_IN

1.5

5

pF

1

CINDIF_IN

DIF_IN differential clock inputs

1.5

2.7

pF

1,4

COUT

Output pin capacitance

6

pF

1

C lk Stabilization

TSTAB

From VDD Power-Up and after input clock

stabilization or de-assertion of PD# to 1st clock

1ms

1,2

Input SS Modulation

Frequency

fMODIN

Allowable Frequency

(Triangular Modulation)

30

33

kHz

1

OE# Latency

tLATOE#

D IF start after OE# assertion

DIF stop after OE# deassertion

1

3

cycles

1,3

Tdrive_PD#

tDRVPD

DIF output enable after

PD# de-assertion

300

us

1,3

Tfall

t

F

Fall time of control inputs

5

ns

1,2

Trise

t

R

R ise time of control inputs

5

ns

1,2

SMBus Input Low Voltage

VIL SMB

0.8

V

1

SMBus Input High Voltage

V

IHSM B

2.1

V

DD SMB

V1

SMBus Output Low Voltage

VOL SMB

@ IPULLUP

0.4

V

1

SMBus Sink Current

IPULLUP

@ VOL

4mA

1

Nominal Bus Voltage

VDDSMB

3V to 5V +/- 10%

2.7

5.5

V

1

SCLK/SD ATA Rise Time

t

RSMB

(Max VIL - 0.15) to (Min VIH + 0.15)

1000

ns

1

SCLK/SDATA Fall Time

t

FSMB

(Min VIH + 0.15) to (Max VIL - 0.15)

300

ns

1

SMBus Operating Frequency

fMAX SMB

Maximum SMBus operating frequency

100

kHz

1,5

1

Guaranteed by design and characterization, not 100% tested in production.

2

C ontrol input must be monotonic from 20% to 80% of input swing.

5The differential input clock must be running for the SMBus to be active

Ambient Operating

Temperature

Input Current

3Time from deassertion until outputs are >200 mV

4DIF_IN input

Capacitance

Input Frequency

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9DB833AFLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DBL411AGLFT | LOW SKEW CLOCK DRIVER, PDSO20 |

| 9DBL411AKLFT | LOW SKEW CLOCK DRIVER, PQCC20 |

| 9DBL411AGLF | LOW SKEW CLOCK DRIVER, PDSO20 |

| 9DBL411BKILF | LOW SKEW CLOCK DRIVER, PQCC20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9DB833AFLFT | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB833AGILF | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB833AGILFT | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB833AGLF | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB833AGLFT | 功能描述:時(shí)鐘緩沖器 8 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。