- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄24830 > 935270667118 (NXP SEMICONDUCTORS) PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF資料下載

參數(shù)資料

| 型號(hào): | 935270667118 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封裝: | 4.40 MM, 0.40 MM PITCH, PLASTIC, MO-153, SOT-480-1, TVSOP-48 |

| 文件頁(yè)數(shù): | 13/15頁(yè) |

| 文件大小: | 113K |

| 代理商: | 935270667118 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)

Philips Semiconductors

Product data

PCKV857

70–190 MHz differential 1:10 clock driver

2002 Sep 13

7

AC CHARACTERISTICS

GND = 0 V; tr = tf ≤ 2.5 ns; CL = 50 pF; RL = 1 k

SYMBOL

PARAMETER

WAVEFORM

CONDITION

LIMITS

UNIT

SYMBOL

PARAMETER

WAVEFORM

CONDITION

MIN

TYP

MAX

UNIT

t(O)

Static phase offset

Figure 1

–150

0

150

ps

tSK(O)

Output clock skew

Figure 2

—

75

ps

tSLR(O)

Output clock skew rate

Figure 3

1

—

2

V/ns

tJIT(PER)

Jitter (period)

Figure 4

fO = 67 MHz to 200 MHz

–75

—

75

ps

tJIT(CC)

Jitter (cycle-to-cycle)

Figure 5

fO = 67 MHz to 200 MHz

–75

—

75

ps

tJIT(HPER)

Half-period jitter

Figure 6

–100

—

100

ps

tPLH1

Low to high level

propagation delay

Test mode/CLK to any

output

—

3.7

—

ns

tPHL1

High to low level

propagation delay

Test mode/CLK to any

output

—

3.7

—

ns

NOTE:

1. Refers to transition of noninverting output.

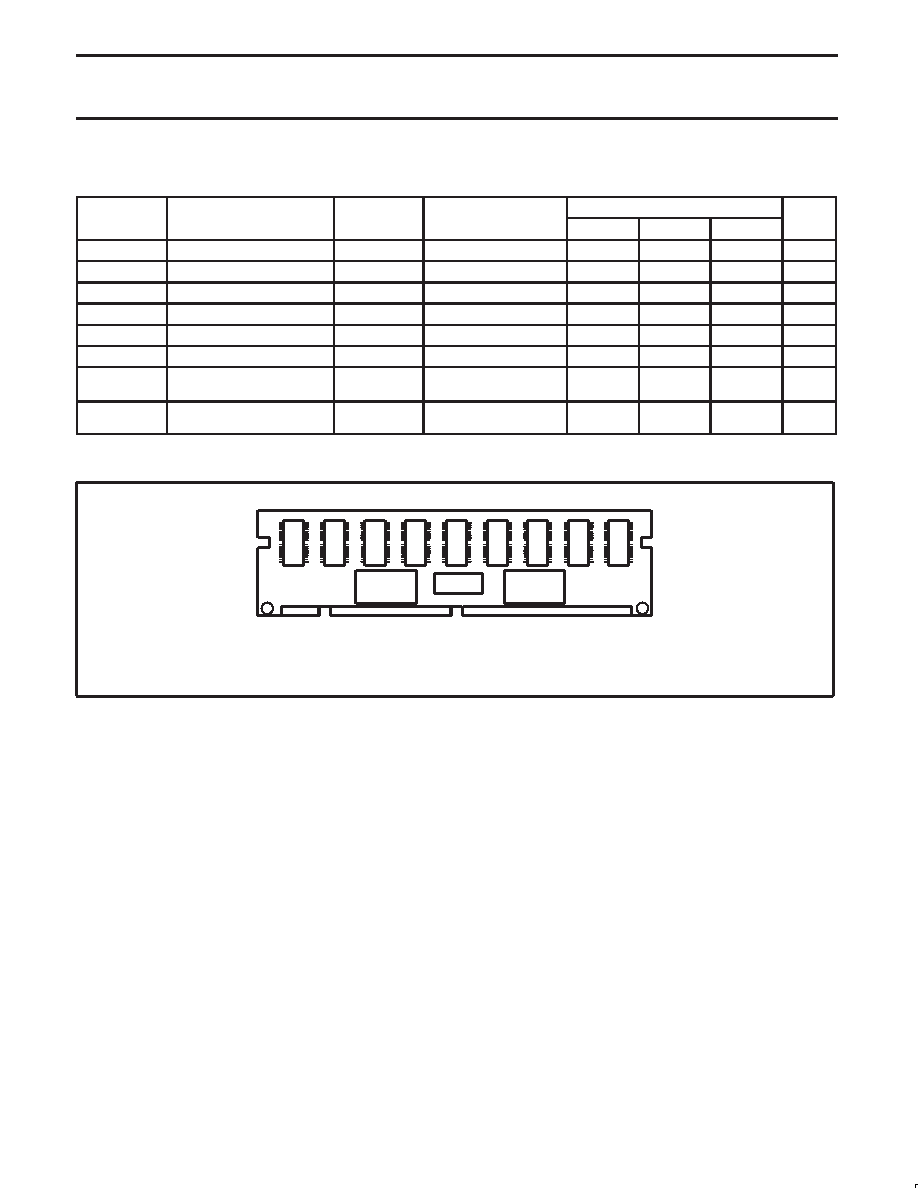

The PLL clock distribution device and SSTL registered drivers reduce

signal loads on the memory controller and prevent timing delays and

waveform distortions that would cause unreliable operation

SW00688

SDRAM

SSTL16877

or

SSTV16857

PCKV857

FRONT SIDE

SSTL16877

or

SSTV16857

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935269132118 | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 935269202112 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 935269193112 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 935269192112 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 935269192118 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

| 935270792551 | 制造商:NXP Semiconductors 功能描述:IC BUFF DVR TRI-ST 16BIT 56VFBGA |

| 935270792557 | 制造商:NXP Semiconductors 功能描述:IC BUFF DVR TRI-ST 16BIT 56VFBGA |

| 935270793551 | 制造商:NXP Semiconductors 功能描述:IC BUS TRCVR 3-ST 16BIT 56VFBGA |

| 935270793557 | 制造商:NXP Semiconductors 功能描述:IC BUS TRCVR 3-ST 16BIT 56VFBGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。